System Control

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

4-167

ID021414

Non-Confidential

Must be interpreted with ID_MMFR0, ID_MMFR2, and ID_MMFR3.

See:

•

Memory Model Feature Register 0

on page 4-165

.

•

Memory Model Feature Register 2

on page 4-168

.

•

Memory Model Feature Register 3

on page 4-170

.

Configurations

ID_MMFR1 is architecturally mapped to AArch64 register

ID_MMFR1_EL1.

There is one copy of this register that is used in both Secure and

Non-secure states.

Attributes

ID_MMFR1 is a 32-bit register.

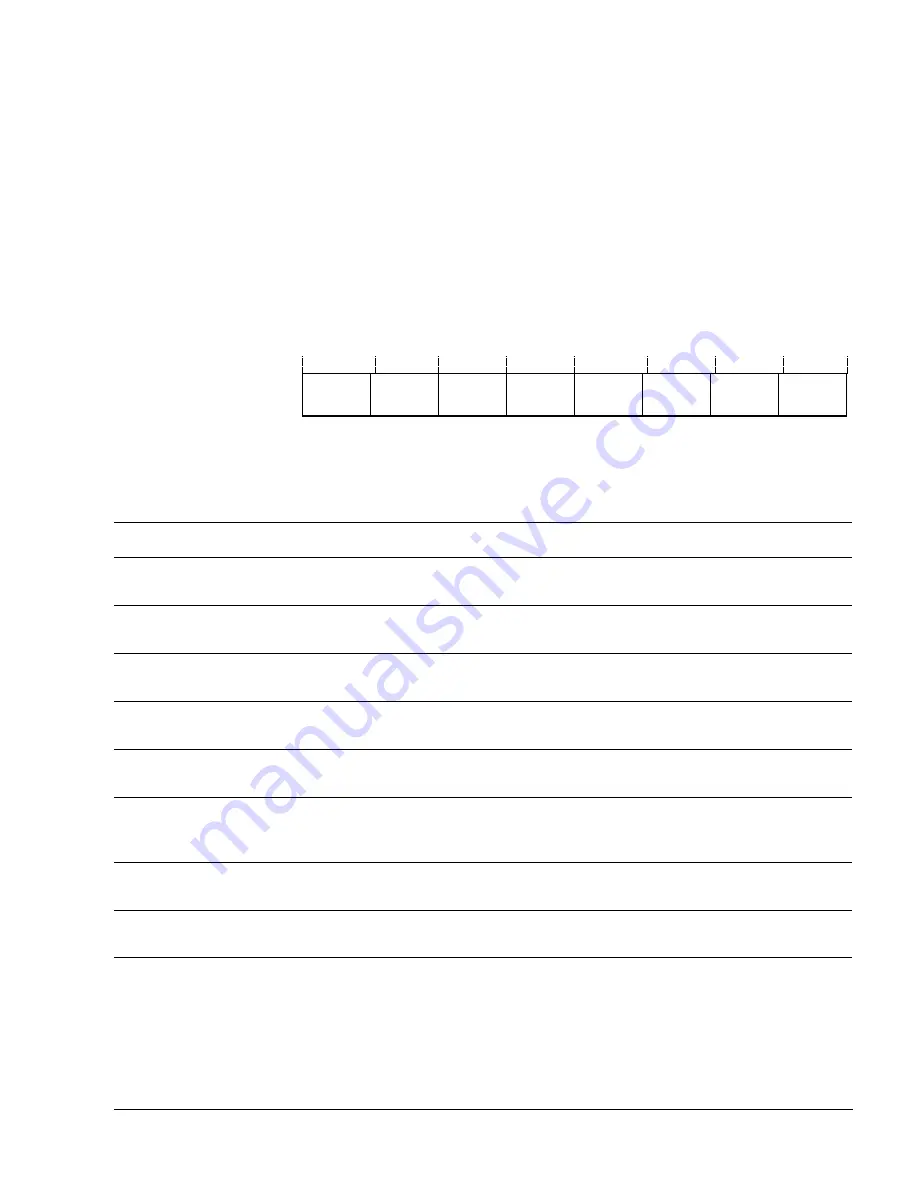

Figure 4-83

shows the ID_MMFR1 bit assignments.

Figure 4-83 ID_MMFR1 bit assignments

Table 4-162

shows the ID_MMFR1 bit assignments.

To access the ID_MMFR1:

MRC p15, 0, <Rt>, c0, c1, 5; Read ID_MMFR1 into Rt

31

12 11

8 7

0

BPred

4 3

28 27

2423

20 19

16 15

L1TstCln

L1Uni

L1Hvd

L1UniSW

L1HvdSW

L1UniVA

L1HvdVA

Table 4-162 ID_MMFR1 bit assignments

Bits

Name

Function

[31:28]

BPred

Indicates branch predictor management requirements:

0x4

For execution correctness, branch predictor requires no flushing at any time.

[27:24]

L1TstCln

Indicates the supported L1 Data cache test and clean operations, for Harvard or unified cache implementation:

0x0

None supported.

[23:20]

L1Uni

Indicates the supported entire L1 cache maintenance operations, for a unified cache implementation:

0x0

None supported.

[19:16]

L1Hvd

Indicates the supported entire L1 cache maintenance operations, for a Harvard cache implementation:

0x0

None supported.

[15:12]

L1UniSW

Indicates the supported L1 cache line maintenance operations by set/way, for a unified cache implementation:

0x0

None supported.

[11:8]

L1HvdSW

Indicates the supported L1 cache line maintenance operations by set/way, for a Harvard cache

implementation:

0x0

None supported.

[7:4]

L1UniVA

Indicates the supported L1 cache line maintenance operations by MVA, for a unified cache implementation:

0x0

None supported.

[3:0]

L1HvdVA

Indicates the supported L1 cache line maintenance operations by MVA, for a Harvard cache implementation:

0x0

None supported.