Embedded Trace Macrocell

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

13-42

ID021414

Non-Confidential

•

Whether TRCSTALLCTLR is supported and if so whether it

supports trace overflow prevention and supports stall control of the

processor.

Usage constraints

There are no usage constraints.

Configurations

Available in all configurations.

Attributes

See the register summary in

Table 13-3 on page 13-10

.

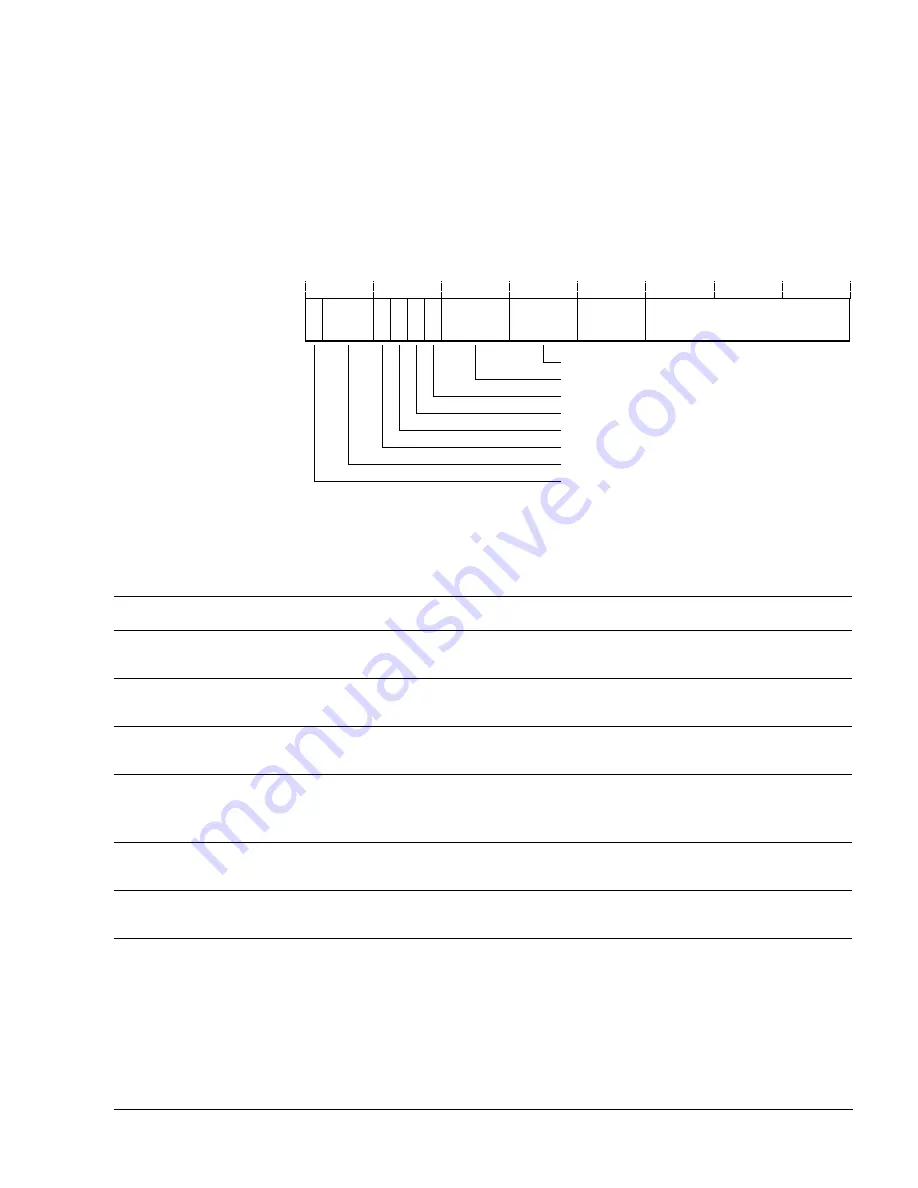

Figure 13-36

shows the TRCIDR3 bit assignments.

Figure 13-36 TRCIDR3 bit assignments

Table 13-37

shows the TRCIDR3 bit assignments.

31

0

25 24

16 15

11

12

5 4

CCITMIN

30

28

20 19

RES

0

23

27 26

EXLEVEL_S

EXLEVEL_NS

NOOVERFLOW

NUMPROC

SYSSTALL

STALLCTL

SYNCPR

TRCERR

Table 13-37 TRCIDR3 bit assignments

Bits

Name

Function

[31]

NOOVERFLOW

Indicates whether TRCSTALLCTLR.NOOVERFLOW is implemented:

0

TRCSTALLCTLR.NOOVERFLOW is not implemented.

[30:28]

NUMPROC

Indicates the number of cores available for tracing:

0b000

The trace unit can trace one processor, ETM trace unit sharing not supported.

[27]

SYSSTALL

Indicates whether stall control is implemented:

1

The system supports processor stall control.

[26]

STALLCTL

Indicates whether TRCSTALLCTLR is implemented:

1

TRCSTALLCTLR is implemented.

This field is used in conjunction with SYSSTALL.

[25]

SYNCPR

Indicates whether there is a fixed synchronization period:

0

TRCSYNCPR is read-write so software can change the synchronization period.

[24]

TRCERR

Indicates whether TRCVICTLR.TRCERR is implemented:

1

TRCVICTLR.TRCERR is implemented.

[23:20]

EXLEVEL_NS

Each bit controls whether instruction tracing in Non-secure state is implemented for the corresponding

exception level:

0b0111

Instruction tracing is implemented for Non-secure EL0, EL1 and EL2 exception levels.