Cross Trigger

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

14-8

ID021414

Non-Confidential

14.5

Cross trigger register descriptions

This section describes the Cortex-A53 MPCore Cross Trigger registers. The

Cross trigger

register summary

on page 14-5

provides cross-references to the individual registers.

14.5.1

CTI Device Identification Register

The CTIDEVID characteristics are:

Purpose

Describes the CTI component to the debugger.

Usage constraints

The accessibility of CTIDEVID by condition code is:

Table 14-4 on page 14-7

describes the condition codes.

Configurations

CTIDEVID is in the Debug power domain.

Attributes

See the register summary in

Table 14-3 on page 14-5

.

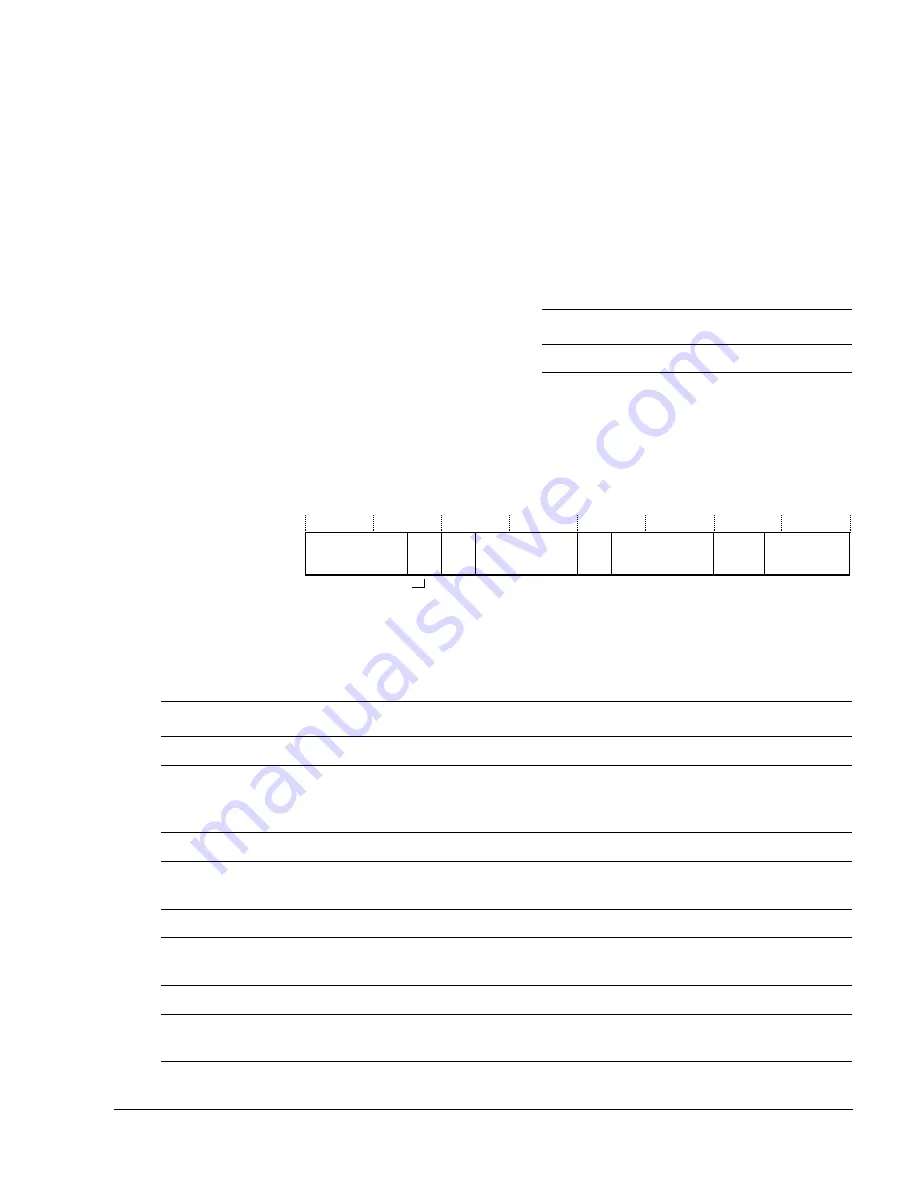

Figure 14-2

shows the CTIDEVID bit assignments.

Figure 14-2 CTIDEVID bit assignments

Table 14-6

shows the CTIDEVID bit assignments.

Off DLK

OSLK

EDAD

SLK

Default

-

-

-

-

RO

RO

31

0

NUMCHAN

15 14 13

INOUT

4

7 6 5

8

16

21

22

23

24

25

26

RES

0

RES

0

NUMTRIG

EXTMAXNUM

RES

0

RES

0

Table 14-6 CTIDEVID bit assignments

Bits

Name

Function

[31:26]

-

Reserved,

RES

0.

[25:24]

INOUT

Input and output options. Indicates the presence of an input gate. The possible values are:

0b00

CTIGATE does not mask propagation of input events from external channels.

0b01

CTIGATE masks propagation of input events from external channels.

[23:22]

-

Reserved,

RES

0.

[21:16]

NUMCHAN

Number of channels implemented. This value is:

0b00100

Four channels implemented.

[15:14]

-

Reserved,

RES

0.

[13:8]

NUMTRIG

Number of triggers implemented. This value is:

0b01000

Eight triggers implemented.

[7:5]

-

Reserved,

RES

0.

[4:0]

EXTMAXNUM

Maximum number of external triggers implemented. This value is:

0b00000

No external triggers implemented.