System Control

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

4-267

ID021414

Non-Confidential

Attributes

HVBAR is a 32-bit register.

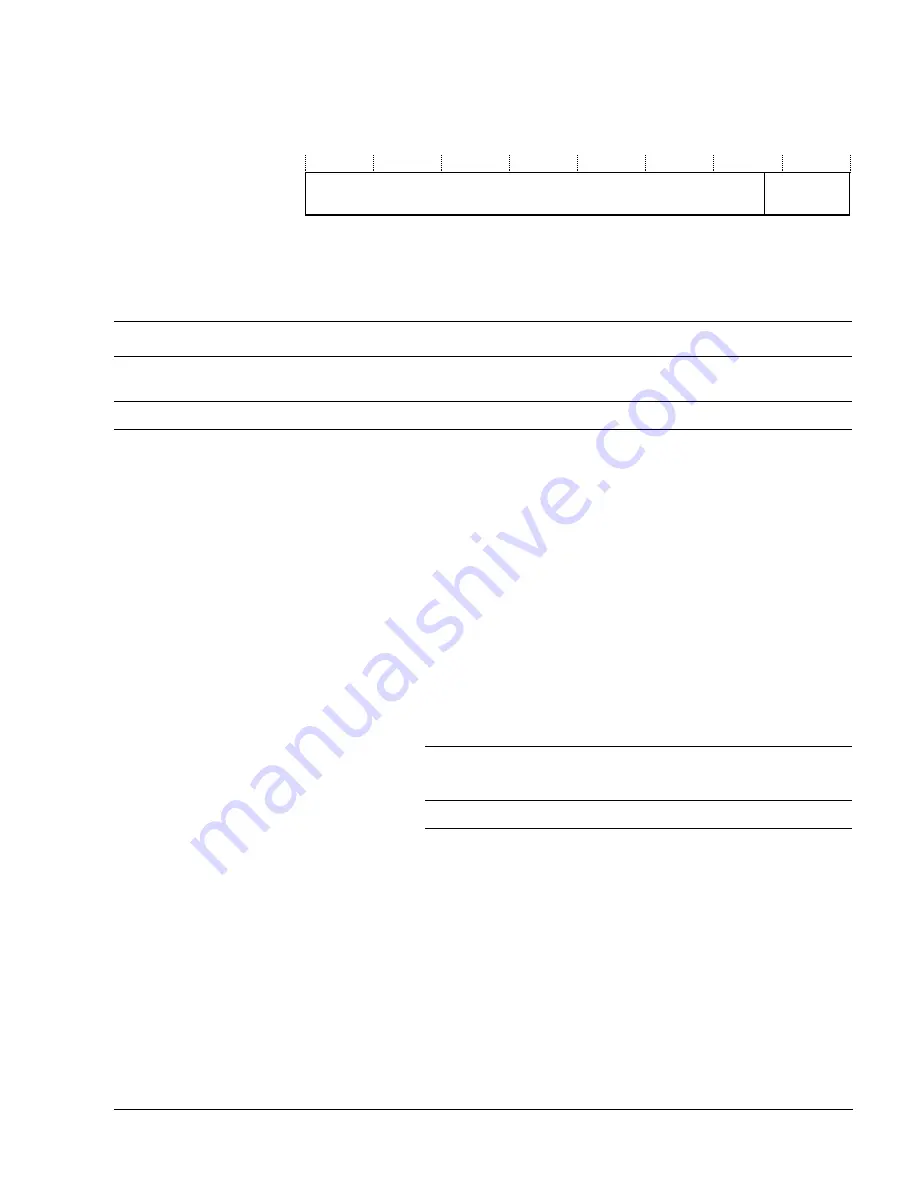

Figure 4-138

shows the HVBAR bit assignments.

Figure 4-138 HVBAR bit assignments

Table 4-242

shows the HVBAR bit assignments.

To access the HVBAR:

MRC p15, 4, <Rt>, c12, c0, 0 ; Read HVBAR into Rt

MCR p15, 4, <Rt>, c12, c0, 0 ; Write Rt to HVBAR

4.5.74

FCSE Process ID Register

The processor does not implement

Fast Context Switch Extension

(FCSE), so this register is

always

RES

0.

4.5.75

L2 Auxiliary Control Register

The L2ACTLR characteristics are:

Purpose

Provides configuration and control options for the L2 memory system.

Usage constraints

This register is accessible as follows:

You can write to this register only when the L2 memory system is idle.

ARM recommends that you write to this register after a powerup reset

before the MMU is enabled and before any ACE, CHI or ACP traffic has

begun.

If the register must be modified after a powerup reset sequence, to idle the

L2 memory system, you must take the following steps:

1.

Disable the MMU from each core followed by an ISB to ensure the

MMU disable operation is complete, then followed by a DSB to

drain previous memory transactions.

2.

Ensure that the system has no outstanding AC channel coherence

requests to the Cortex-A53 processor.

RES

0

31

0

Vector Base Address

4

5

Table 4-242 HVBAR bit assignments

Bits

Name

Function

[31:5]

Vector Base Address

Bits[31:5] of the base address of the exception vectors, for exceptions taken in this exception level.

Bits[4:0] of an exception vector are the exception offset.

[4:0]

-

Reserved,

RES

0.

EL0

(NS)

EL0

(S)

EL1

(NS)

EL1

(S)

EL2

EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

-

-

RW

RW

RW

RW

RW