Programmers Model

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

3-10

ID021414

Non-Confidential

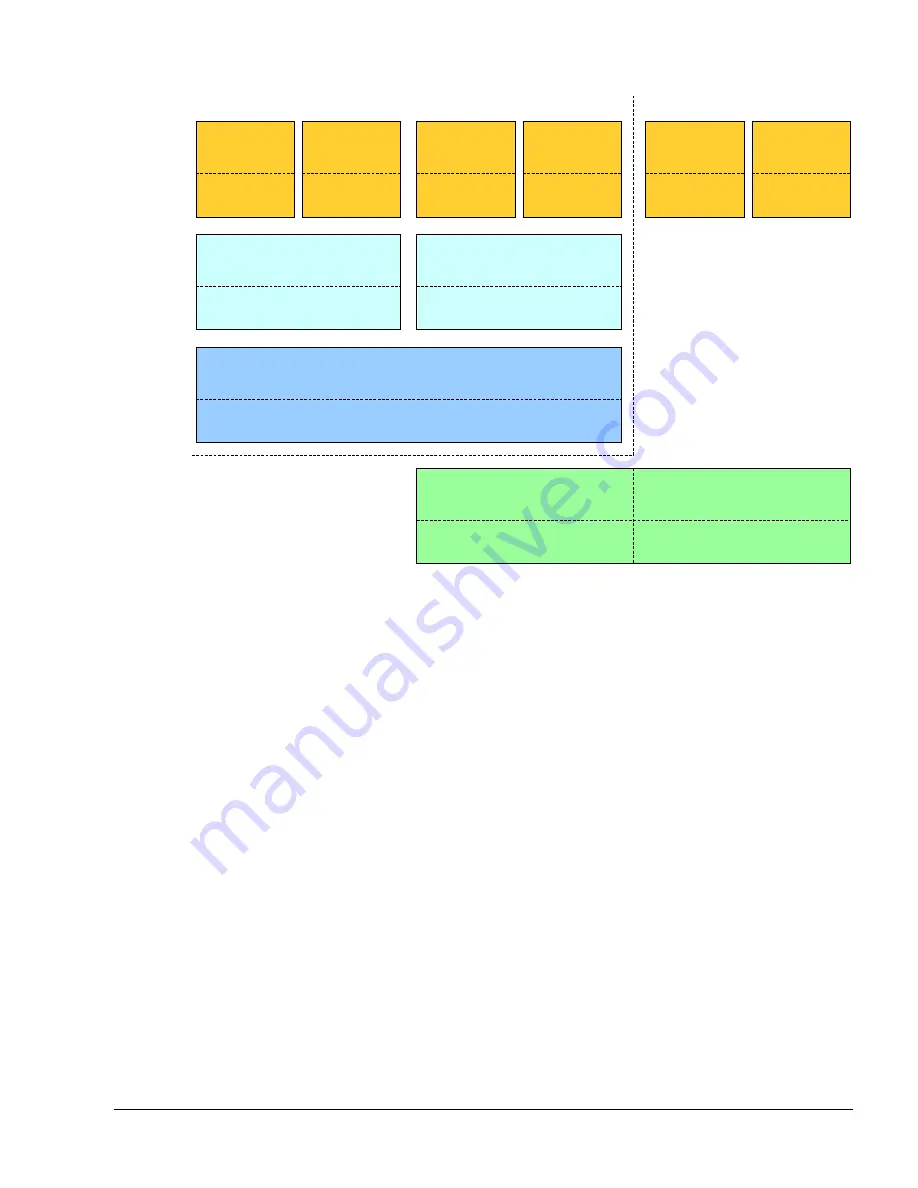

Figure 3-2 ARMv8 security model when EL3 is using AArch32

For more information about the AArch32 processor modes see

AArch32 execution modes

.

3.2.7

Instruction set state

The processor instruction set state determines the instruction set that the processor executes. The

instruction sets depend on the execution state:

AArch64

AArch64 state supports only a single instruction set, called A64. This is a

fixed-width instruction set that uses 32-bit instruction encodings.

AArch32

AArch32 state supports the following instruction sets:

A32

This is a fixed-length instruction set that uses 32-bit instruction

encodings. Before the introduction of ARMv8, it was called the ARM

instruction set.

T32

This is a variable-length instruction set that uses both 16-bit and 32-bit

instruction encodings. Before the introduction of ARMv8, it was

called the Thumb instruction set state.

3.2.8

AArch32 execution modes

ARMv7 and earlier versions of the ARM architecture define a set of named processor modes,

including modes that correspond to different exception types. For compatibility, AArch32 state

retains these processor modes.

Secure App2

Secure App1

App2

App1

App2

App1

Guest OS1

Guest OS2

Hypervisor

AArch32

EL0

EL1

EL2

EL3

Non-secure state

Secure state

Monitor

Modes:

Secure monitor

Secure OS

Hyp

Modes:

AArch32

System, FIQ, IRQ,

Supervisor, Abort, Undefined

Modes:

AArch32

AArch32

System, FIQ, IRQ,

Supervisor, Abort, Undefined

Modes:

User

Modes:

AArch32

User

Modes:

AArch32

User

Modes:

AArch32

User

Modes:

AArch32

User

Modes:

AArch32

User

Modes:

AArch32

System, FIQ, IRQ,

Supervisor, Abort, Undefined

Modes: