Functional Description

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

2-9

ID021414

Non-Confidential

2.3

Clocking and resets

The following sections describe clocking and resets:

•

Clocks

.

•

Input synchronization

on page 2-13

.

•

Resets

on page 2-14

.

2.3.1

Clocks

The Cortex-A53 processor has a single clock input,

CLKIN

. All cores in the Cortex-A53

processor and the SCU are clocked with a distributed version of

CLKIN

.

The Cortex-A53 processor has the following clock enable signals:

•

PCLKENDBG

.

•

ACLKENM

on page 2-10

.

•

ACLKENS

on page 2-10

.

•

SCLKEN

on page 2-11

.

•

ATCLKEN

on page 2-12

.

•

CNTCLKEN

on page 2-12

.

PCLKENDBG

The processor includes an APB interface to access the debug and performance monitoring

registers. Internally this interface is driven from

CLKIN

. A separate enable signal,

PCLKENDBG

, is provided to enable the external APB bus to be driven at a lower frequency,

that must be an integer ratio of

CLKIN

. If the debug infrastructure in the system is required to

be fully asynchronous to the processor clock, you can use a synchronizing component to

connect the external AMBA APB to the processor.

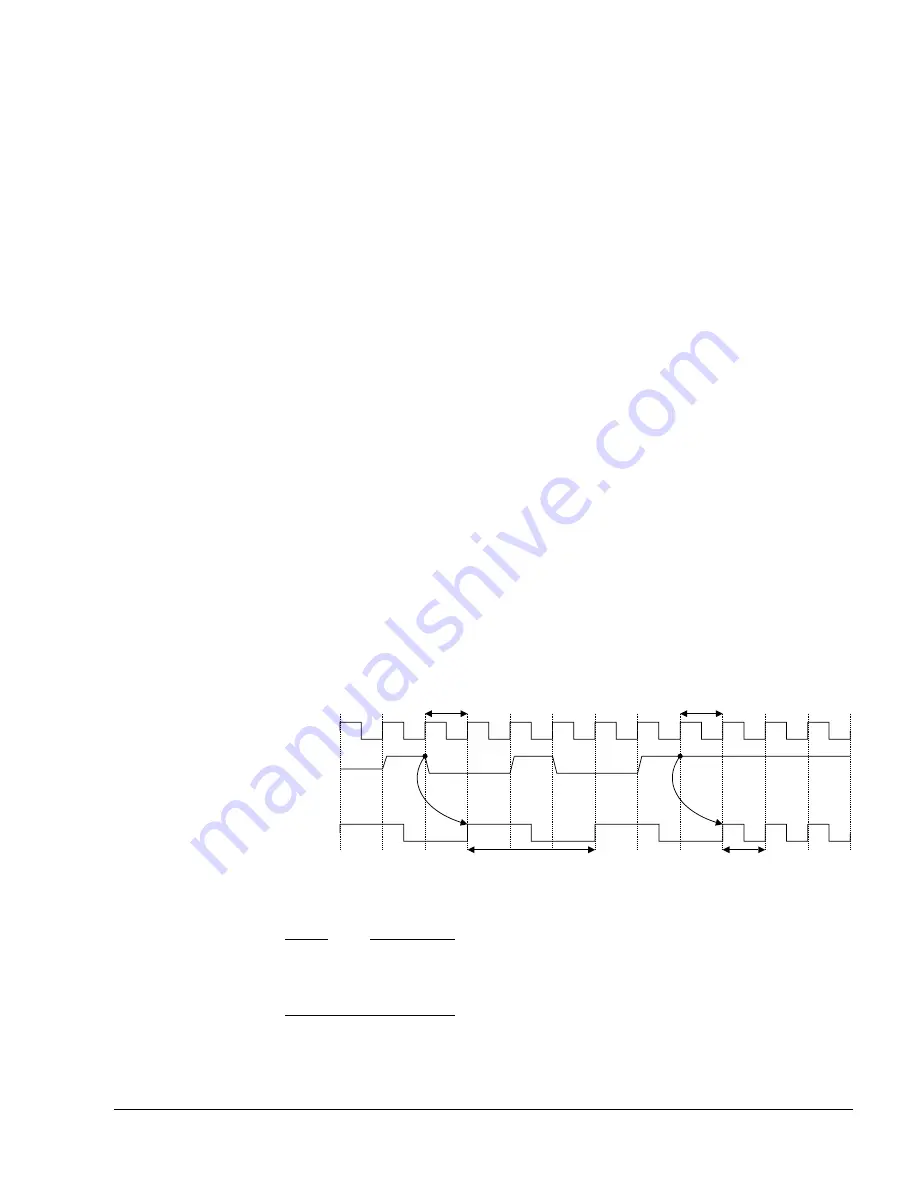

Figure 2-2

shows a timing example of

PCLKENDBG

that changes the

CLKIN

to

PCLK

frequency ratio from 3:1 to 1:1.

Figure 2-2 PCLKENDBG with CLKIN:PCLK ratio changing from 3:1 to 1:1

Note

Figure 2-2

shows the timing relationship between the debug APB clock,

PCLK

and

PCLKENDBG

, where

PCLKENDBG

asserts one clock cycle before the rising edge of

PCLK

.

It is important that the relationship between

PCLK

and

PCLKENDBG

is maintained.

PCLK

PCLKENDBG

asserts one

CLKIN

cycle before the rising edge of

PCLK

1

CLKIN

cycle

CLKIN

:

PCLK

= 3:1

CLKIN

:

PCLK

= 1:1

PCLKENDBG

CLKIN

1

CLKIN

cycle