System Control

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

4-105

ID021414

Non-Confidential

Table 4-97

on page 4-104

shows the FAR_EL2 bit assignments.

To access the FAR_EL2:

MRS <Xt>, FAR_EL2 ; Read EL2 Fault Address Register

MSR FAR_EL2, <Xt> ; Write EL2 Fault Address Register

4.3.63

Hypervisor IPA Fault Address Register, EL2

The HPFAR_EL2 characteristics are:

Purpose

Holds the faulting IPA for some aborts on a stage 2 translation taken to

EL2.

Usage constraints

This register is accessible as follows:

Configurations

HPFAR_EL2[31:0] is mapped to AArch32 register HPFAR. See

Hyp IPA

Fault Address Register

on page 4-250

.

Attributes

HPFAR_EL2 is a 64-bit register.

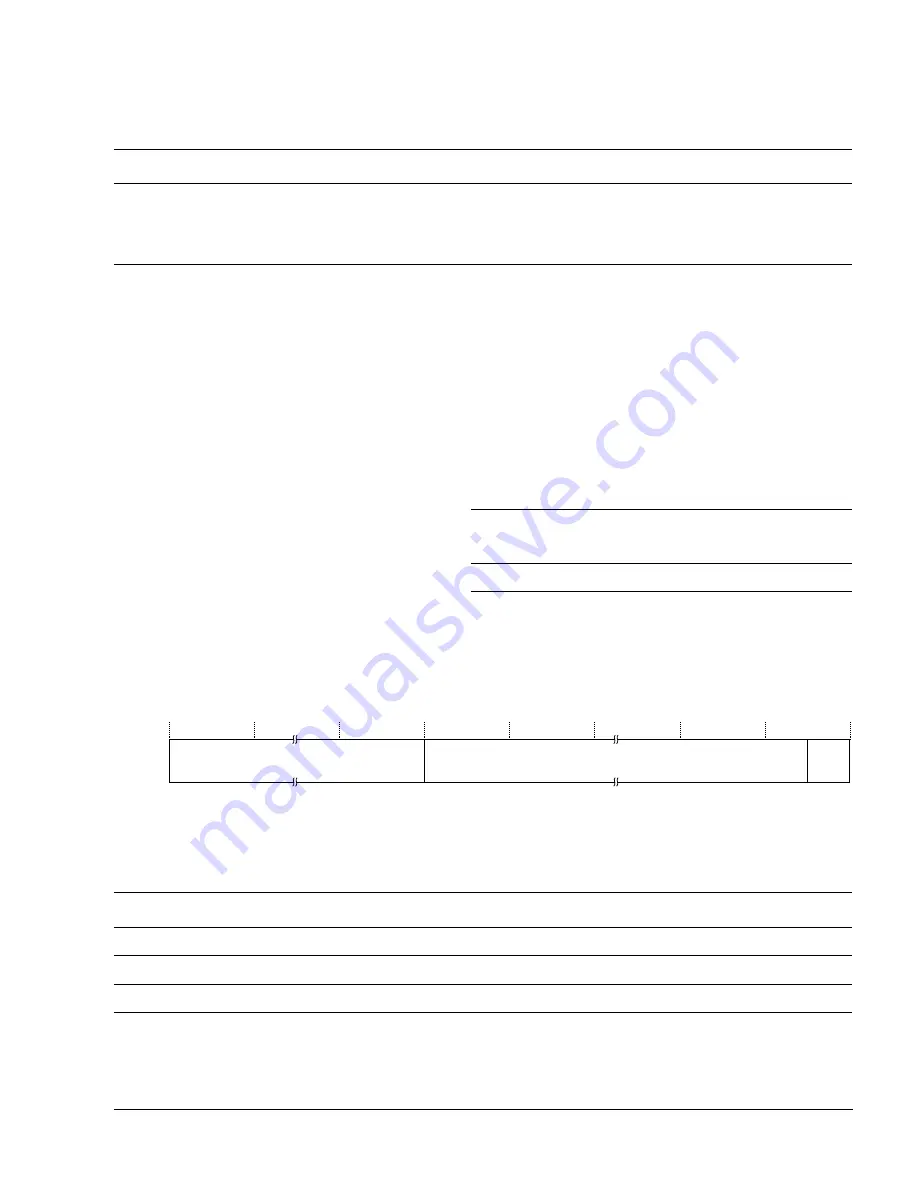

Figure 4-57

shows the HPFAR_EL2 bit assignments.

Figure 4-57 HPFAR_EL2 bit assignments

Table 4-98

on page 4-104

shows the HPFAR_EL2 bit assignments.

To access the HPFAR_EL:

MRS <Xt>, HPFAR_EL2 ; Read EL2 Fault Address Register

MSR HPFAR_EL2, <Xt> ; Write EL2 Fault Address Register

Table 4-97 FAR_EL2 bit assignments

Bits

Name

Function

[63:0]

VA

The faulting Virtual Address for all synchronous instruction or data aborts, or an exception from a misaligned PC,

taken in EL2.

If a memory fault that sets the FAR is generated from one of the data cache instructions, this field holds the address

specified in the register argument of the instruction.

EL0

EL1

(NS)

EL1

(S)

EL2

EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

-

-

-

RW

RW

RW

39

40

0

63

FIPA[47:12]

RES

0

3

4

RES

0

Table 4-98 HPFAR_EL2 bit assignments

Bits

Name

Function

[63:40]

-

Reserved,

RES

0.

[39:4]

FIPA[47:12]

Bits [47:12] of the faulting intermediate physical address. The equivalent upper bits in this field are

RES

0.

[3:0]

-

Reserved,

RES

0.