Embedded Trace Macrocell

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

13-26

ID021414

Non-Confidential

The TRCVICTLR can be accessed through the internal memory-mapped interface and the

external debug interface, offset

0x080

.

13.8.14 ViewInst Include-Exclude Control Register

The TRCVIIECTLR characteristics are:

Purpose

Defines the address range comparators that control the ViewInst

Include/Exclude control.

Usage constraints

•

You must always program this register as part of trace unit

initialization.

•

Accepts writes only when the trace unit is disabled.

Configurations

Available in all configurations.

Attributes

See the register summary in

Table 13-3 on page 13-10

.

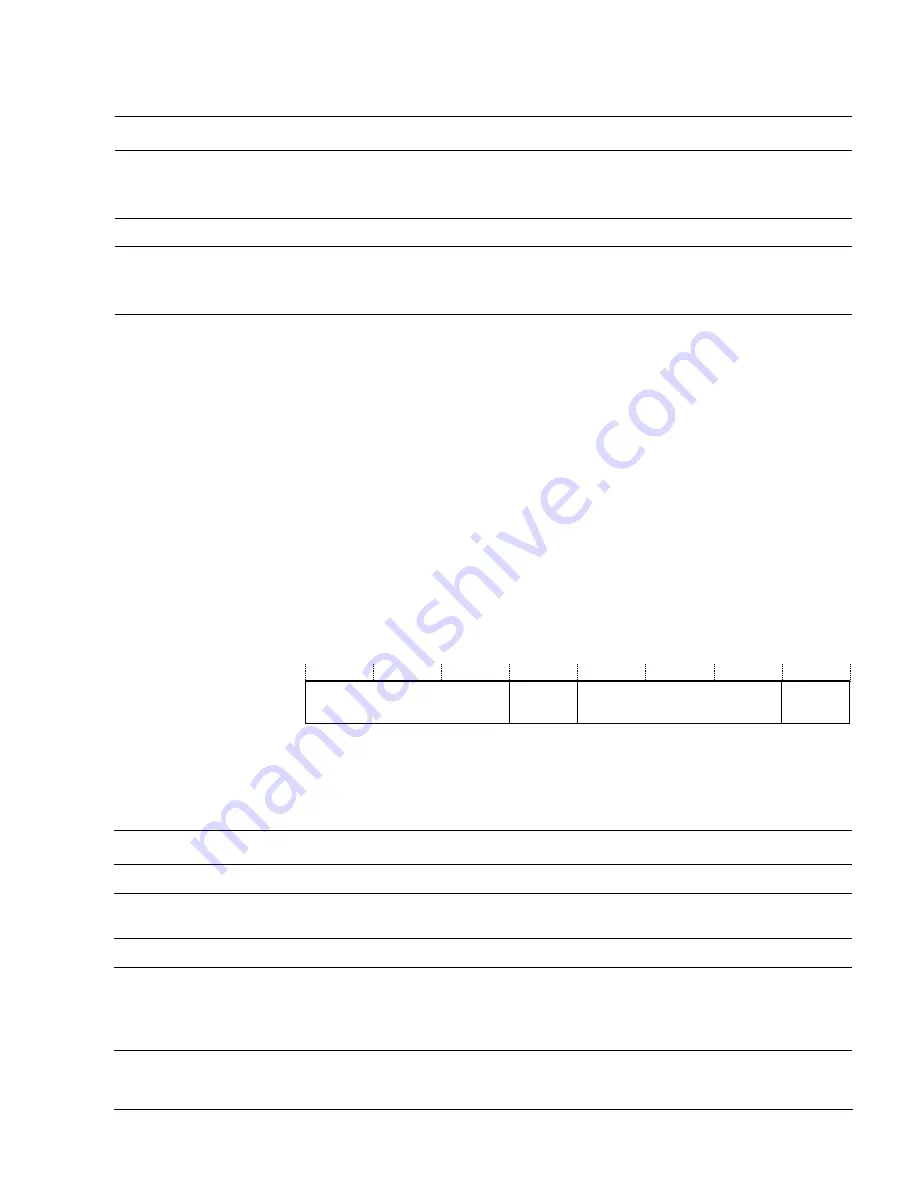

Figure 13-16

shows the TRCVIIECTLR bit assignments.

Figure 13-16 TRCVIIECTLR bit assignments

Table 13-17

shows the TRCVIIECTLR bit assignments.

[7]

TYPE

Selects the resource type for the viewinst event:

0

Single selected resource.

1

Boolean combined resource pair.

[6:4]

-

Reserved,

RES

0.

[3:0]

SEL

Selects the resource number to use for the viewinst event, based on the value of TYPE:

When TYPE is 0, selects a single selected resource from 0-15 defined by bits[3:0].

When TYPE is 1, selects a Boolean combined resource pair from 0-7 defined by bits[2:0].

Table 13-16 TRCVICTLR bit assignments (continued)

Bits

Name

Function

31

0

RES

0

EXCLUDE

16 15

RES

0

INCLUDE

19

20

3

4

Table 13-17 TRCVIIECTLR bit assignments

Bits

Name

Function

[31:20]

-

Reserved,

RES

0.

[19:16]

EXCLUDE

Defines the address range comparators for ViewInst exclude control. One bit is provided for each

implemented Address Range Comparator.

[15:4]

-

Reserved,

RES

0.

[3:0]

INCLUDE

Defines the address range comparators for ViewInst include control.

Selecting no include comparators indicates that all instructions must be included. The exclude control

indicates which ranges must be excluded.

One bit is provided for each implemented Address Range Comparator.