APPENDIX B POWER SAVING

330

EPSON

S1C17001 TECHNICAL MANUAL

This section describes clock systems that can be controlled via software and power-saving control details. For more

information on control registers and control methods, refer to the respective module sections.

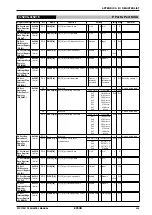

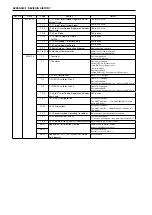

System SLEEP (All clocks stopped)

• Execute

slp

command

Execute

the

slp

command when the entire system can be stopped. The CPU switches to SLEEP mode and

the system clocks stop. This also stops all peripheral circuits using clocks. Starting up the CPU from SLEEP

mode is therefore limited to startup using ports (described later).

System clocks

• Clock source selection (OSC module)

Select between OSC3 and OSC1 for the system clock source. Reduce current consumption by selecting the

OSC1 clock when low-speed processing is possible.

• OSC3 oscillation circuit stop (OSC module)

Operate the oscillation circuit comprising the system clock source. Where possible, stop the other circuit.

You can reduce current consumption by using OSC1 as the system clock and stopping the OSC3 oscillation

circuit.

CPU clock (CCLK)

• Execute the

halt

command

Execute

the

halt

command when program execution by the CPU is not required—for example, when only

the display is required or for interrupt standby. The CPU switches to HALT mode and suspends operations,

but the peripheral circuits maintain the status in place at the time of the

halt

command, enabling use of pe-

ripheral circuits for timers and interrupts. You can reduce power consumption even further by suspending un-

necessary peripheral circuits before executing the halt command. The CPU is started from HALT mode using

the port or interrupts from the peripheral circuit operating in HALT mode.

• Low-speed clock gear selection (CLG module)

The CLG module can reduce CPU clock speeds to between 1/1 and 1/8 of the system clock via the clock gear

settings. Reduce current consumption by operating the CPU at the minimum speed required for applications.

Peripheral clock (PCLK)

• PCLK stop (CLG module)

Stop the PCLK clock feed from the CLG to peripheral circuits if none of the following peripheral circuits is

required.

Peripheral circuits operating with PCLK

• Prescaler (PWM & capture timer, remote controller, P port)

• UART

• 8-bit timer

• 16-bit timer Ch.0 to Ch.2

• Interrupt controller

• SPI

• I

2

C

• P port and port MUX (control register, chattering filter)

• PWM & capture timer

• MISC register

• Remote controller

Содержание S1C17001

Страница 1: ...Technical Manual S1C17001 CMOS 16 BIT SINGLE CHIP MICROCONTROLLER ...

Страница 31: ...3 MEMORY MAP AND BUS CONTROL 22 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 33: ...4 POWER SUPPLY VOLTAGE 24 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 63: ...6 INITERRUPT CONTROLLER 54 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 87: ...8 CLOCK GENERATOR CLG 78 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 91: ...9 PRESCALER PSC 82 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 133: ...11 16 BIT TIMER T16 124 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 185: ...14 8 BIT OSC1 TIMER T8OSC1 176 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 211: ...16 STOPWATCH TIMER SWT 202 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 219: ...17 WATCHDOG TIMER WDT 210 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 241: ...18 UART 232 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 277: ...20 I2 C 268 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 297: ...21 REMOTE CONTROLLER REMC 288 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 303: ...22 ON CHIP DEBUGGER DBG 294 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 313: ...25 PACKAGE 304 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...