ii

EPSON

S1C17001 TECHNICAL MANUAL

6.6 HALT and SLEEP Mode Cancellation by Interrupt Factors ........................................... 6-11

6.7 Control Register Details ................................................................................................. 6-12

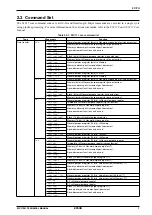

0x4300: Interrupt Flag Register (ITC_IFLG) .............................................................................. 6-13

0x4302: Interrupt Enable Register (ITC_EN) ............................................................................. 6-15

0x4304: ITC Control Register (ITC_CTL) .................................................................................. 6-16

0x4306: External Interrupt Level Setup Register 0 (ITC_ELV0) ................................................ 6-17

0x4308: External Interrupt Level Setup Register 1 (ITC_ELV1) ................................................ 6-18

0x430a: External Interrupt Level Setup Register 2 (ITC_ELV2) ................................................ 6-19

0x430c: External Interrupt Level Setup Register 3 (ITC_ELV3) ................................................ 6-20

0x430e: Internal Interrupt Level Setup Register 0 (ITC_ILV0) ................................................... 6-21

0x4310: Internal Interrupt Level Setup Register 1 (ITC_ILV1) ................................................... 6-22

0x4312: Internal Interrupt Level Setup Register 2 (ITC_ILV2) ................................................... 6-23

0x4314: Internal Interrupt Level Setup Register 3 (ITC_ILV3) ................................................... 6-24

6.8 Precautions .................................................................................................................... 6-25

7 Oscillator Circuit (OSC) .................................................................................................7-1

7.1 OSC Module Configuration ............................................................................................. 7-1

7.2 OSC3 Oscillator Circuit ................................................................................................... 7-2

7.3 OSC1 Oscillator Circuit ................................................................................................... 7-4

7.4 System Clock Switching ................................................................................................. 7-5

7.5 8-bit OSC1 Timer Clock Control ..................................................................................... 7-6

7.6 Clock External Output (FOUT3, FOUT1) ......................................................................... 7-7

7.7 RESET and NMI Input Noise Filters ................................................................................ 7-9

7.8 Control Register Details ................................................................................................. 7-10

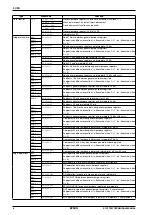

0x5060: Clock Source Select Register (OSC_SRC) ................................................................. 7-11

0x5061: Oscillation Control Register (OSC_CTL) ..................................................................... 7-12

0x5062: Noise Filter Enable Register (OSC_NFEN) ................................................................. 7-13

0x5064: FOUT Control Register (OSC_FOUT) ......................................................................... 7-14

0x5065: T8OSC1 Clock Control Register (OSC_T8OSC1) ...................................................... 7-15

7.9 Precautions .................................................................................................................... 7-16

8 Clock Generator (CLG) ..................................................................................................8-1

8.1 Clock Generator Configuration ....................................................................................... 8-1

8.2 CPU Core Clock (CCLK) Control .................................................................................... 8-2

8.3 Peripheral Module Clock (PCLK) Control ........................................................................ 8-3

8.4 Control Register Details .................................................................................................. 8-4

0x5080: PCLK Control Register (CLG_PCLK) ........................................................................... 8-5

0x5081: CCLK Control Register (CLG_CCLK) .......................................................................... 8-6

8.5 Precautions ..................................................................................................................... 8-7

9 Prescaler (PSC) ..............................................................................................................9-1

9.1 Prescaler Configuration .................................................................................................. 9-1

9.2 Control Register Details .................................................................................................. 9-2

0x4020: Prescaler Control Register (PSC_CTL) ........................................................................ 9-2

9.3 Precautions ..................................................................................................................... 9-3

10 Input/Output Port (P) ..................................................................................................10-1

10.1 Input/Output Port Configuration .................................................................................. 10-1

10.2 Input/Output Port Pin Function Selection (Port MUX) ................................................. 10-2

10.3 Data Input/Output ........................................................................................................ 10-3

10.4 Pull-up Control ............................................................................................................. 10-4

10.5 Input Interface Level .................................................................................................... 10-5

10.6 P0 Port Chattering Filter Function ................................................................................ 10-6

10.7 Port Input Interrupt ....................................................................................................... 10-7

Содержание S1C17001

Страница 1: ...Technical Manual S1C17001 CMOS 16 BIT SINGLE CHIP MICROCONTROLLER ...

Страница 31: ...3 MEMORY MAP AND BUS CONTROL 22 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 33: ...4 POWER SUPPLY VOLTAGE 24 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 63: ...6 INITERRUPT CONTROLLER 54 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 87: ...8 CLOCK GENERATOR CLG 78 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 91: ...9 PRESCALER PSC 82 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 133: ...11 16 BIT TIMER T16 124 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 185: ...14 8 BIT OSC1 TIMER T8OSC1 176 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 211: ...16 STOPWATCH TIMER SWT 202 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 219: ...17 WATCHDOG TIMER WDT 210 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 241: ...18 UART 232 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 277: ...20 I2 C 268 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 297: ...21 REMOTE CONTROLLER REMC 288 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 303: ...22 ON CHIP DEBUGGER DBG 294 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 313: ...25 PACKAGE 304 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...