19 SPI

236

EPSON

S1C17001 TECHNICAL MANUAL

19.4 Data Transfer Condition Settings

The SPI module can be set to Master or Slave modes. The SPI clock polarity and phase can also be set via the

SPI_CTL register.

The data length is fixed at 8 bits.

Note: Make sure the SPI module is halted (when SPEN/SPI_CTL register = 0) before Master/Slave

mode selection and clock condition settings.

∗

SPEN

: SPI Enable Bit in the SPI Control (SPI_CTL) Register (D0/0x4326)

Master/Slave mode selection

MSSL (D1/SPI_CTL register) is used to set the SPI module to Master mode or Slave mode. Setting MSSL to 1

sets Master mode; setting it to 0 (default) sets Slave mode. In Master mode, data is transferred using the inter-

nal clock. In Slave mode, data is transferred by inputting the master device clock.

∗

MSSL

: Master/Slave Mode Select Bit in the SPI Control (SPI_CTL) Register (D1/0x4326)

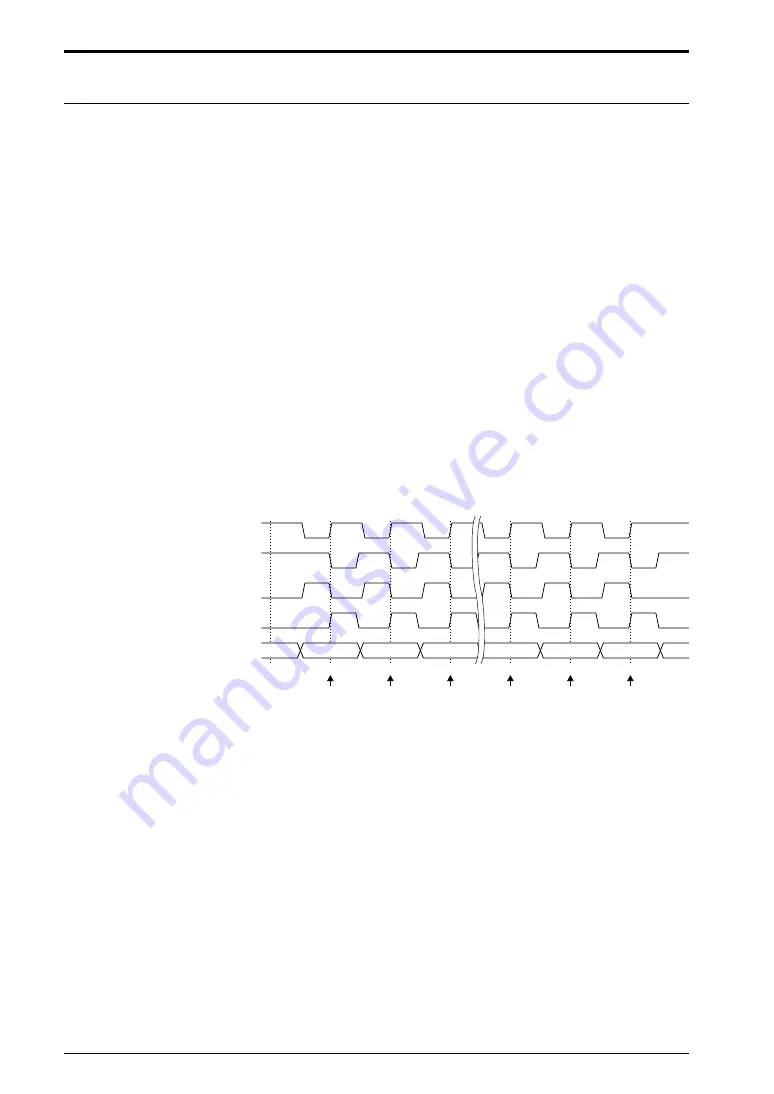

SPI clock polarity and phase settings

The SPI clock polarity is selected by CPOL (D2/SPI_CTL register). Setting CPOL to 1 treats the SPI clock as

active Low; setting it to 0 (default) treats it as active High.

∗

CPOL

: Clock Polarity Select Bit in the SPI Control (SPI_CTL) Register (D2/0x4326)

The SPI clock phase is selected by CPHA (D3/SPI_CTL register).

∗

CPHA

: Clock Phase Select Bit in the SPI Control (SPI_CTL) Register (D3/0x4326)

As shown below, these control bits set transfer timing.

SPICLK(CPOL = 1, CPHA = 1)

SPICLK(CPOL = 1, CPHA = 0)

SPICLK(CPOL = 0, CPHA = 1)

SPICLK(CPOL = 0, CPHA = 0)

SDI/SDO

Receive data load timing

to shift register

D7 (MSB)

D0 (LSB)

Figure 19.4.1: Clock and data transfer timing

Содержание S1C17001

Страница 1: ...Technical Manual S1C17001 CMOS 16 BIT SINGLE CHIP MICROCONTROLLER ...

Страница 31: ...3 MEMORY MAP AND BUS CONTROL 22 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 33: ...4 POWER SUPPLY VOLTAGE 24 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 63: ...6 INITERRUPT CONTROLLER 54 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 87: ...8 CLOCK GENERATOR CLG 78 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 91: ...9 PRESCALER PSC 82 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 133: ...11 16 BIT TIMER T16 124 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 185: ...14 8 BIT OSC1 TIMER T8OSC1 176 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 211: ...16 STOPWATCH TIMER SWT 202 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 219: ...17 WATCHDOG TIMER WDT 210 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 241: ...18 UART 232 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 277: ...20 I2 C 268 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 297: ...21 REMOTE CONTROLLER REMC 288 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 303: ...22 ON CHIP DEBUGGER DBG 294 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 313: ...25 PACKAGE 304 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...