21 REMOTE CONTROLLER (REMC)

S1C17001 TECHNICAL MANUAL

EPSON

277

Falling edge interrupt

Generated when the REMI pin input signal changes from High to Low, this interrupt request sets the interrupt

flag REMRIF (D2/REMC_IFLG register) to 1 within the REMC.

When data is being received, the data length counter can be operated between this interrupt and a falling edge

interrupt to calculate the received data pulse width from that count value.

∗

REMFIF

: Falling Edge Interrupt Flag in the REMC Interrupt Flag (REMC_IFLG) Register (D2/0x5347)

To use this interrupt, set REMFIE (D2/REMC_IMSK register) to 1. If REMFIE is set to 0 (default), REMFIF is

not set to 1 and the interrupt request for this factor is not sent to the ITC.

∗

REMFIE

: Falling Edge Interrupt Enable Bit in the REMC Interrupt Mask (REMC_IMSK) Register (D2/0x5346)

When REMFIF is set to 1, REMC outputs an interrupt request to the ITC. This interrupt request signal sets the

REMC interrupt flag to 1 within the ITC, generating an interrupt if the ITC and S1C17 core interrupt conditions

are met.

REMFIF should be inspected as part of the REMC interrupt processing routine to determine whether the

REMC interrupt is attributable to input signal falling edge.

The interrupt factor should be cleared as part of the interrupt processing routine by resetting both the ITC

REMC interrupt flag and REMC module REMFIF (i.e., setting both to 1).

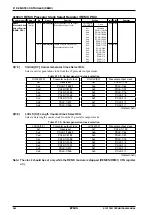

REMC interrupt ITC register

The REMC module outputs an interrupt signal to the ITC if an interrupt factor permitted by the previous set-

tings occurs. To generate an REMC interrupt, the interrupt level and interrupt permission should be set using

the ITC register.

The ITC control bits for the REMC are given below.

ITC internal interrupt flag

∗

IIFT5

: Remote Controller Interrupt Flag in the Interrupt Flag (ITC_IFLG) Register (D13/0x4300)

ITC internal interrupt enable bit

∗

IIEN5

: Remote Controller Interrupt Enable Bit in the Interrupt Enable (ITC_EN) Register (D13/0x4302)

ITC internal interrupt level setting bit

∗

IILV5[2:0]

: REMC Interrupt Level Bits in the Internal Interrupt Level Setup (ITC_ILV2) Register 2 (D[10:8]/0x4312)

Interrupt signals from the REMC module set IIFT5 to 1. If IIEN5 is set to 1 here, the ITC sends an interrupt

request to the S1C17 core. To block interrupts by the REMC module, set IIEN5 to 0. IIFT5 is set to 1 by the

interrupt signal from the REMC module, regardless of the IIEN5 setting (even if set to 0).

IILV5[2:0] sets the REMC interrupt level (0 to 7).

The S1C17 core accepts interrupts when all of the following conditions are met:

• The interrupt enable bit is set to 1.

• The PSR (S1C17 core internal processor status register) IE (interrupt enable) bit is set to 1.

• The REMC interrupt has a higher interrupt level set than that set for the PSR IL (interrupt level).

• There are no other interrupt factors, including NMI, with higher priority.

For detailed information on these interrupt registers and operations when interrupts occur, refer to “6 Interrupt

Controller (ITC).”

Interrupt vectors

The REMC interrupt vector numbers and vector addresses are as listed below.

Vector number: 17 (0x11)

Vector

address:

0x8040

Содержание S1C17001

Страница 1: ...Technical Manual S1C17001 CMOS 16 BIT SINGLE CHIP MICROCONTROLLER ...

Страница 31: ...3 MEMORY MAP AND BUS CONTROL 22 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 33: ...4 POWER SUPPLY VOLTAGE 24 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 63: ...6 INITERRUPT CONTROLLER 54 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 87: ...8 CLOCK GENERATOR CLG 78 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 91: ...9 PRESCALER PSC 82 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 133: ...11 16 BIT TIMER T16 124 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 185: ...14 8 BIT OSC1 TIMER T8OSC1 176 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 211: ...16 STOPWATCH TIMER SWT 202 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 219: ...17 WATCHDOG TIMER WDT 210 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 241: ...18 UART 232 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 277: ...20 I2 C 268 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 297: ...21 REMOTE CONTROLLER REMC 288 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 303: ...22 ON CHIP DEBUGGER DBG 294 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 313: ...25 PACKAGE 304 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...