S1C17001 TECHNICAL MANUAL

EPSON

i

- Contents -

1 Overview ........................................................................................................................1-1

1.1 Features .......................................................................................................................... 1-1

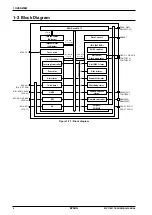

1-2 Block Diagram ................................................................................................................ 1-2

1.3 Pins ................................................................................................................................. 1-3

1.3.1 Pinout Diagram ................................................................................................. 1-3

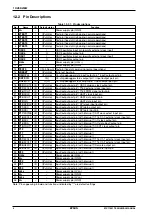

1.3.2 Pin Descriptions ................................................................................................ 1-4

2 CPU ................................................................................................................................2-1

2.1 S1C17 Core Features ...................................................................................................... 2-1

2.2 CPU Registers ................................................................................................................. 2-2

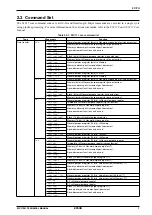

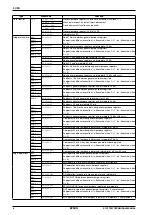

2.3 Command Set ................................................................................................................. 2-3

2.4 Vector Table .................................................................................................................... 2-7

2.5 Processor Information ..................................................................................................... 2-8

3 Memory Map and Bus Control ......................................................................................3-1

3.1 Bus Cycle ........................................................................................................................ 3-2

3.1.1 Access Size Restrictions .................................................................................. 3-2

3.1.2 Command Execution Cycle Restrictions .......................................................... 3-2

3.2 Internal ROM Area ........................................................................................................... 3-3

3.2.1 Internal ROM ..................................................................................................... 3-3

3.2.2 ROM Read Access Cycle Settings ................................................................... 3-3

0x5320: ROM Control Register (MISC_FL) ............................................................................... 3-3

3.3 Internal RAM Area ........................................................................................................... 3-4

3.3.1 Internal RAM ..................................................................................................... 3-4

3.4 Internal Peripheral Circuit Area ....................................................................................... 3-5

3.4.1 Internal Peripheral Circuit Area 1 (0x4000 onward) .......................................... 3-5

3.4.2 Internal Peripheral Circuit Area 2 (0x5000 onward) .......................................... 3-5

3.4.3 I/O Map ............................................................................................................. 3-6

3.5 Core I/O Reserved Area .................................................................................................. 3-9

4 Power Supply Voltage ...................................................................................................4-1

5 Initial Reset ....................................................................................................................5-1

5.1 Initial Reset Factors ........................................................................................................ 5-1

5.1.1 #RESET pin ....................................................................................................... 5-1

5.1.2 P0 Port Key-Entry Reset ................................................................................... 5-2

5.1.3 Reset by Watchdog Timer ................................................................................ 5-2

5.2 Initial Reset Sequence .................................................................................................... 5-3

5.3 Initial Settings at Initial Resetting .................................................................................... 5-4

6 Interrupt Controller (ITC) ...............................................................................................6-1

6.1 ITC Configuration ............................................................................................................ 6-1

6.2 Vector Table .................................................................................................................... 6-2

6.3 Maskable Interrupt Control ............................................................................................. 6-3

6.3.1 ITC Enable ........................................................................................................ 6-3

6.3.2 Interrupt Request from Peripheral Module and Interrupt Flag .......................... 6-3

6.3.3 Interrupt Permission/Prohibition ....................................................................... 6-4

6.3.4 Processing for Multiple Interrupts .................................................................... 6-5

6.3.5 Interrupt Trigger Modes .................................................................................... 6-6

6.3.6 S1C17 Core Interrupt Processing ..................................................................... 6-8

6.4 NMI .................................................................................................................................. 6-9

6.5 Software Interrupts ........................................................................................................ 6-10

Содержание S1C17001

Страница 1: ...Technical Manual S1C17001 CMOS 16 BIT SINGLE CHIP MICROCONTROLLER ...

Страница 31: ...3 MEMORY MAP AND BUS CONTROL 22 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 33: ...4 POWER SUPPLY VOLTAGE 24 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 63: ...6 INITERRUPT CONTROLLER 54 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 87: ...8 CLOCK GENERATOR CLG 78 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 91: ...9 PRESCALER PSC 82 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 133: ...11 16 BIT TIMER T16 124 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 185: ...14 8 BIT OSC1 TIMER T8OSC1 176 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 211: ...16 STOPWATCH TIMER SWT 202 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 219: ...17 WATCHDOG TIMER WDT 210 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 241: ...18 UART 232 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 277: ...20 I2 C 268 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 297: ...21 REMOTE CONTROLLER REMC 288 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 303: ...22 ON CHIP DEBUGGER DBG 294 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 313: ...25 PACKAGE 304 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...