1 OVERVIEW

S1C17001 TECHNICAL MANUAL

EPSON

1

1 Overview

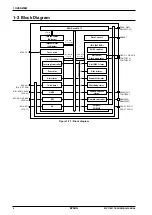

The S1C7001 is a 16-bit MCU featuring high-speed low-power operations, compact dimensions, wide address

space, and on-chip ICE. In addition to the S1C17 CPU core, it incorporates 32 Kbytes of ROM, 2 Kbytes of RAM,

a serial interface supporting various sensors such as UART, SPI, and I

2

C high-bit-rate and IrDA1.0 compatibility,

8-bit timer, 16-bit timer, PWM & capture timer, clock timer, stopwatch timer, watchdog timer, and 28 general pur-

pose input/output ports.

It allows 8.2 MHz high-speed operation at an operating voltage of just 1.8 V, and executes single commands using

a single clock with 16-bit RISC processing.

1.1 Features

The main features of the S1C17001 are listed below.

●

7

1

C

1

S

e

r

o

c

U

P

C

C

S

I

R

t

i

b

-

6

1

l

a

n

i

g

i

r

o

n

o

s

p

E

•

U

P

C

●

Main (OSC3) oscillator circuit

• Crystal oscillator circuit, ceramic oscillator circuit, or external

clock input 8.2 MHz (max)

●

Sub (OSC1) oscillator circuit

• Crystal oscillator circuit or external clock input 32.768 kHz (typ)

●

s

e

t

y

b

K

2

3

•

M

O

R

l

a

n

r

e

t

n

I

●

s

e

t

y

b

K

2

•

M

A

R

l

a

n

r

e

t

n

I

●

l

a

r

e

n

e

g

t

i

b

-

8

2

.

x

a

M

•

t

r

o

p

t

u

p

t

u

o

/

t

u

p

n

I

purpose input/output (shared with periph-

eral circuit input/output pins)

●

.

h

c

1

)

e

v

a

l

s

/

r

e

t

s

a

m

(

I

P

S

•

e

c

a

f

r

e

t

n

i

l

a

i

r

e

S

.

h

c

1

)

e

l

b

i

t

a

p

m

o

c

0

.

1

A

D

r

I

(

T

R

A

U

•

I

•

2

C (master)

1ch.

.

h

c

1

)

C

M

E

R

(

r

e

l

l

o

r

t

n

o

c

e

t

o

m

e

R

•

●

.

h

c

1

)

F

8

T

(

r

e

m

i

t

t

i

b

-

8

•

r

e

m

i

T

.

h

c

3

)

6

1

T

(

r

e

m

i

t

t

i

b

-

6

1

•

.

h

c

1

)

E

6

1

T

(

r

e

m

i

t

e

r

u

t

p

a

c

&

M

W

P

•

.

h

c

1

)

T

C

(

r

e

m

i

t

k

c

o

l

C

•

.

h

c

1

)

T

W

S

(

r

e

m

i

t

h

c

t

a

w

p

o

t

S

•

.

h

c

1

)

T

D

W

(

r

e

m

i

t

g

o

d

h

c

t

a

W

•

.

h

c

1

)

1

C

S

O

8

T

(

r

e

m

i

t

1

C

S

O

t

i

b

-

8

•

●

t

e

s

e

R

•

t

p

u

r

r

e

t

n

I

I

M

N

•

)

s

l

e

v

e

l

8

(

4

1

x

t

p

u

r

r

e

t

n

i

e

r

a

w

d

r

a

H

•

●

V

L

(

e

g

a

t

l

o

v

e

r

o

C

•

e

g

a

t

l

o

v

y

l

p

p

u

s

r

e

w

o

P

DD

)

1.65 V to 2.7 V

V

H

(

e

g

a

t

l

o

v

O

/

I

•

DD

)

1.65 V to 3.6 V

●

Operating temperature

• -40°C to 85°C

●

Current consumption (typ.)

• 0.5

μ

A in SLEEP mode

5

.

2

•

μ

A in HALT mode (32 kHz)

0

1

•

μ

A when operating (32 kHz)

0

0

8

1

μ

A when operating (8 MHz)

●

Configuration as shipped

• WCSP-48pin package

●

Mask ROM code development Flash memory • S1C17704 (refer to Appendix E for details)

Содержание S1C17001

Страница 1: ...Technical Manual S1C17001 CMOS 16 BIT SINGLE CHIP MICROCONTROLLER ...

Страница 31: ...3 MEMORY MAP AND BUS CONTROL 22 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 33: ...4 POWER SUPPLY VOLTAGE 24 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 63: ...6 INITERRUPT CONTROLLER 54 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 87: ...8 CLOCK GENERATOR CLG 78 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 91: ...9 PRESCALER PSC 82 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 133: ...11 16 BIT TIMER T16 124 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 185: ...14 8 BIT OSC1 TIMER T8OSC1 176 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 211: ...16 STOPWATCH TIMER SWT 202 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 219: ...17 WATCHDOG TIMER WDT 210 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 241: ...18 UART 232 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 277: ...20 I2 C 268 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 297: ...21 REMOTE CONTROLLER REMC 288 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 303: ...22 ON CHIP DEBUGGER DBG 294 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...

Страница 313: ...25 PACKAGE 304 EPSON S1C17001 TECHNICAL MANUAL This page intentionally left blank ...