A96G140/A96G148/A96A148 User’s manual

15. USI

159

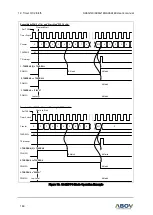

Transmitter consists of a single write buffer, a serial shift register, parity generator and control logic for

handling different serial frame formats. A write buffer allows continuous transfer of data without any

delay between frames.

Receiver is the most complex part of the UART module due to its clock and data recovery units. The

recovery unit is used for asynchronous data reception. In addition to the recovery unit, the receiver

includes a parity checker, a shift register, a two-level receive FIFO (USInDR) and control logic. The

receiver supports the same frame formats as the transmitter and can detect frame error, data overrun

and parity errors.

15.2

USIn UART block diagram

RXDn

Rx

Control

Clock

Recovery

Receive Shift Register

(RXSR)

Data

Recovery

DORn/PEn/FEn

Checker

USInDR[0], USInRX8[0], (Rx)

USInDR[1], USInRX8[1], (Rx)

TXDn

Tx

Control

Stop bit

Generator

Parity

Generator

Transmit Shift Register

(TXSR)

USInDR, USInTX8, (Tx)

USInP[1:0]

M

U

X

LOOPSn

TXCn

TXCIEn

DRIEn

DREn

Empty signal

To interrupt

block

INT_ACK

Clear

RXCn

RXCIEn

WAKEIEn

WAKEn

At Stop mode

To interrupt

block

SCLK

(fx: System clock)

Low level

detector

2

USInS[2:0]

3

USInS[2:0]

3

TXEn

RXEn

DBLSn

USInSB

Baud Rate Generator

USInBD

I

N

T

E

R

N

A

L

B

U

S

L

I

N

E

SCKn

ACK

Control

Clock

Sync Logic

Master

USInMS[1:0]

M

U

X

M

U

X

USInMS[1:0]

USInMS[1:0]

2

2

2

Figure 84. USIn USART Block Diagram (n = 0 and 1)