A96G140/A96G148/A96A148 User’s manual

20 Development tools

263

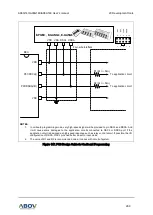

As shown in Figure 142

, when transferring data, a receiver outputs the DSDA to ‘L’ to inform the normal

reception of data. If a receiver outputs DSDA to ‘H’, it means error reception of data.

Figure 142. Acknowledge on Serial Bus

While the Host Debugger executes data communications, if a microcontroller needs communication

delay or process delay, it can request communication delay to the Host Debugger.

Figure 143 shows timing diagrams where a microcontroller requests communication delay to the Host

Debugger. If the microcontroller requests timing delay of the DSCL signal that the Host Debugger

outputs, the microcontroller maintains the DSCL signal to ‘L’ to d

elay the clock change although the

Host Debugger changes the DSCL to ‘H’.

Figure 143. Clock Synchronization during Wait Procedure