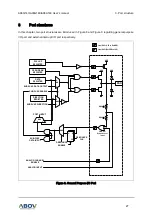

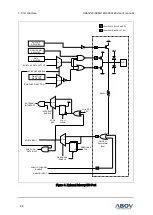

3. Port structure

A96G140/A96G148/A96A148 User’s manual

28

Figure 9. External Interrupt I/O Port

VDD

VDD

VDD

PAD

SUB-FUNC ENABLE

LevelShift (1.8V to ExtVDD)

LevelShift (ExtVDD to 1.8V)

DATA

REGISTER

OPEN DRAIN

REGISTER

PULL-UP

REGISTER

SUB-FUNC DATA OUTPUT

DIRECTION

REGISTER

SUB-FUNC DIRECTION

0

1

MUX

MUX

0

1

0

1

MUX

r

D

CP

Q

DEBOUNCE

CLK

DEBOUNCE

ENABLE

PORTx INPUT

SUB-FUNC

DATA INPUT

ANALOG CHANNEL

ENABLE

ANALOG INPUT

0

1

MUX

r

D

CP

Q

VDD

EXTERNAL

INTERRUPT

INTERRUPT

ENABLE

EDGE

REG

FLAG

CLEAR

POLARITY

REG

R(400

Ω

)

CMOS or

SchmittLevel

Input