A96G140/A96G148/A96A148 User’s manual

12. Timer 0/1/2/3/4/5

143

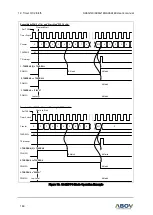

12.6.2

16-bit capture mode

Timer 5 capture mode is set by configuring T5MS[

1:0] as ‘01’.

It uses an internal clock as a clock source.

Basically, the 16-bit timer 5 capture mode has the same function as the 16-bit timer/counter mode, and

the interrupt occurs when T5CNTH/T5CNTL is equal to T5ADRH/T5ADRL. The T5CNTH, T5CNTL

values are automatically cleared by a match signal. It can be cleared by software (T5CC) too.

A timer interrupt in capture mode is very useful when the pulse width of captured signal is wider than

the maximum period of timer. Capture result is loaded into T5BDRH/T5BDRL. In the timer 5 capture

mode, timer 5 output (T5O) waveform is not available.

According to EIPOL0H registers setting, the external interrupt EINT5 function is selected. EINT5 pin

must be set as an input port.

A Match

T5CC

T5EN

P

r

e

s

c

a

l

e

r

fx

M

U

X

fx/2

fx/4

fx/32

fx/128

fx/512

fx/8

fx/1

16-bit Cou nte r

T5CNTH/T5CNTL

16-bit B Data Re gister

T5BDRH/T5BDRL

Clear

HIRC

Comparator

16-bit A Data Re gister

T5ADRH/T5ADRL

T5IFR

S/W

Clear

To i nte rrupt

block

A Match

Buffer Reg ister A

Reload

R

EINT5

T5CNTR

T5EN

3

T5CK[2:0]

Clear

FLAG5

(EIFLAG0.5)

INT_ACK

Clear

To i nte rrupt

block

T5MS[1:0]

2

A Match

T5CC

T5EN

T5EN

T5CRH

1

ADDRES S:1010H

INITIAL VALUE : 0000_0000B

–

T5MS1

T5MS0

–

–

–

T5CC

–

0

1

–

–

–

X

T5CK2

T5CRL

X

ADDRES S:1011H

INITIAL VALUE : 0000_0000B

T5CK1

T5CK0

T5IFR

–

T5POL

–

T5CNTR

X

X

X

–

X

–

X

EIPOL0H[3:2]

2

Figure 72. 16-bit Capture Mode of Timer 5