A96G140/A96G148/A96A148 User’s manual

20 Development tools

261

Packet transmission timing

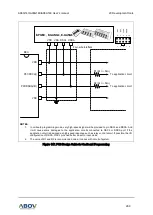

Figure 139 shows a timing diagram of a packet transmission using the OCD communication protocol.

A start bit in the figure means start of a packet and is valid when the

DSDA falls from ‘H’ to ‘L’ while

External Host maintains the

DSCL to ‘H’. After

the valid start bit, communication data is transferred and

received between a Host and a microcontroller.

An end bit means end of the data transmission and is valid when the

DSDA changes from ‘L’ to ‘H’

while a Debugger maintains the

DSCL to ‘H’. Next, the microcontroller places the bus in a wait state

and processes the received data.

Figure 139. Data Transfer on OCD