User Manual

745

Rev. 1.1

2019-03-18

TLE984xQX

Microcontroller with LIN and Power Switches for Automotive Applications

Measurement Core Module (incl. ADC2)

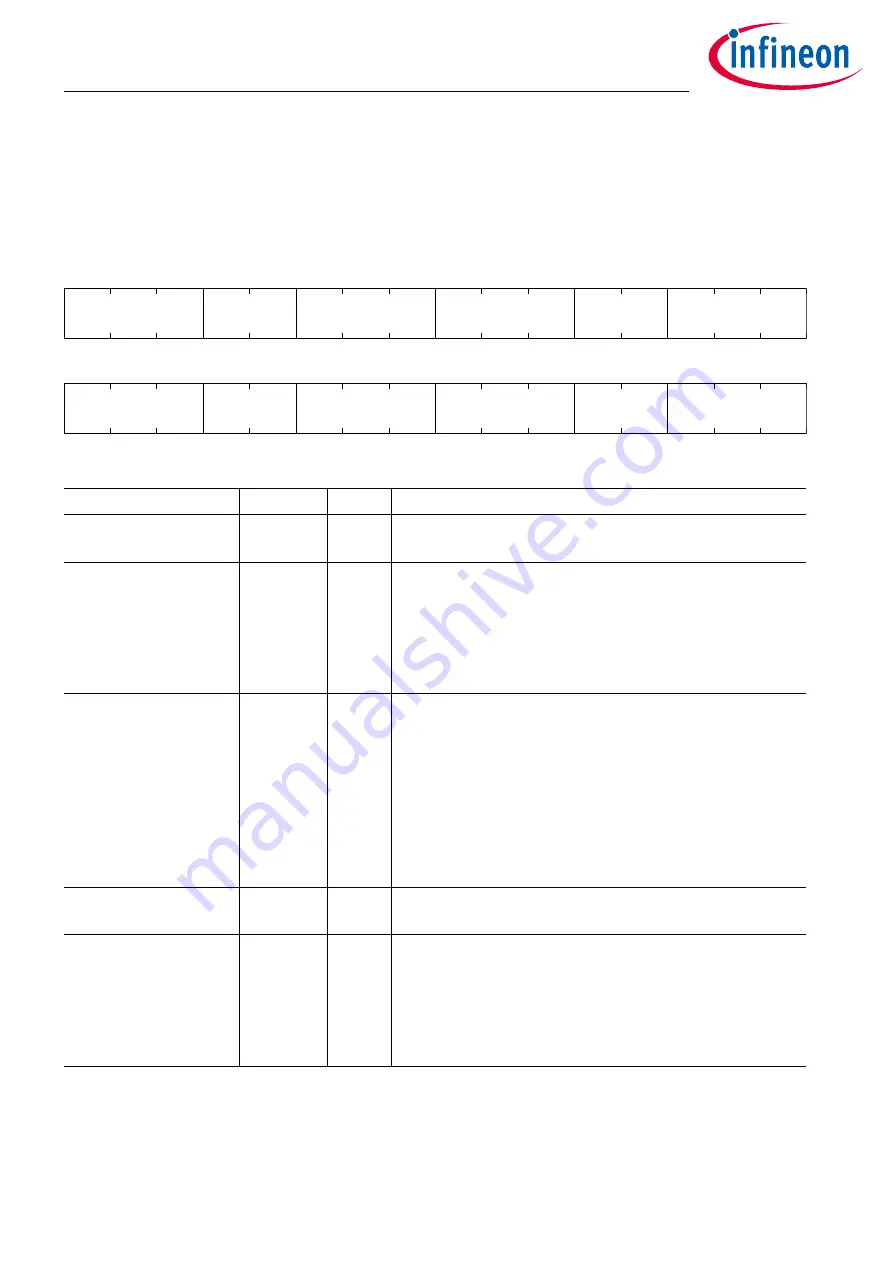

Lower Counter Trigger Level Channel 0 - 3

ADC2_CNT0_3_LOWER

Offset

Reset Value

Lower Counter Trigger Level Channel 0 - 3

98

H

see

Field

Bits

Type

Description

RES

31:29

r

Reserved

Always read as 0

HYST_LO_CH3

28:27

rw

Channel 3 lower hysteresis

0

H

HYSTOFF

, hysteresis switched off

1

H

HYST4

, hysteresis = 4

2

H

HYST8

, hysteresis = 8

3

H

HYST16

, hysteresis = 16

CNT_LO_CH3

26:24

rw

Lower timer trigger threshold channel 3

0

H

1 measurement

1

H

2 measurements

2

H

4 measurements

3

H

8 measurements

4

H

16 measurements

5

H

32 measurements

6

H

63 measurements

7

H

63 measurements

RES

23:21

r

Reserved

Always read as 0

HYST_LO_CH2

20:19

rw

Channel 2 lower hysteresis

0

H

HYSTOFF

, hysteresis switched off

1

H

HYST4

, hysteresis = 4

2

H

HYST8

, hysteresis = 8

3

H

HYST16

, hysteresis = 16

31

29

r

RES

28

27

rw

HYST_LO

_CH3

26

24

rw

CNT_LO_CH3

23

21

r

RES

20

19

rw

HYST_LO

_CH2

18

16

rw

CNT_LO_CH2

15

13

r

RES

12

11

rw

HYST_LO

_CH1

10

8

rw

CNT_LO_CH1

7

5

r

RES

4

3

rw

HYST_LO

_CH0

2

0

rw

CNT_LO_CH0