XC161 Derivatives

Peripheral Units (Vol. 2 of 2)

TwinCAN Module

User’s Manual

21-52

V2.2, 2004-01

TwinCAN_X1, V2.1

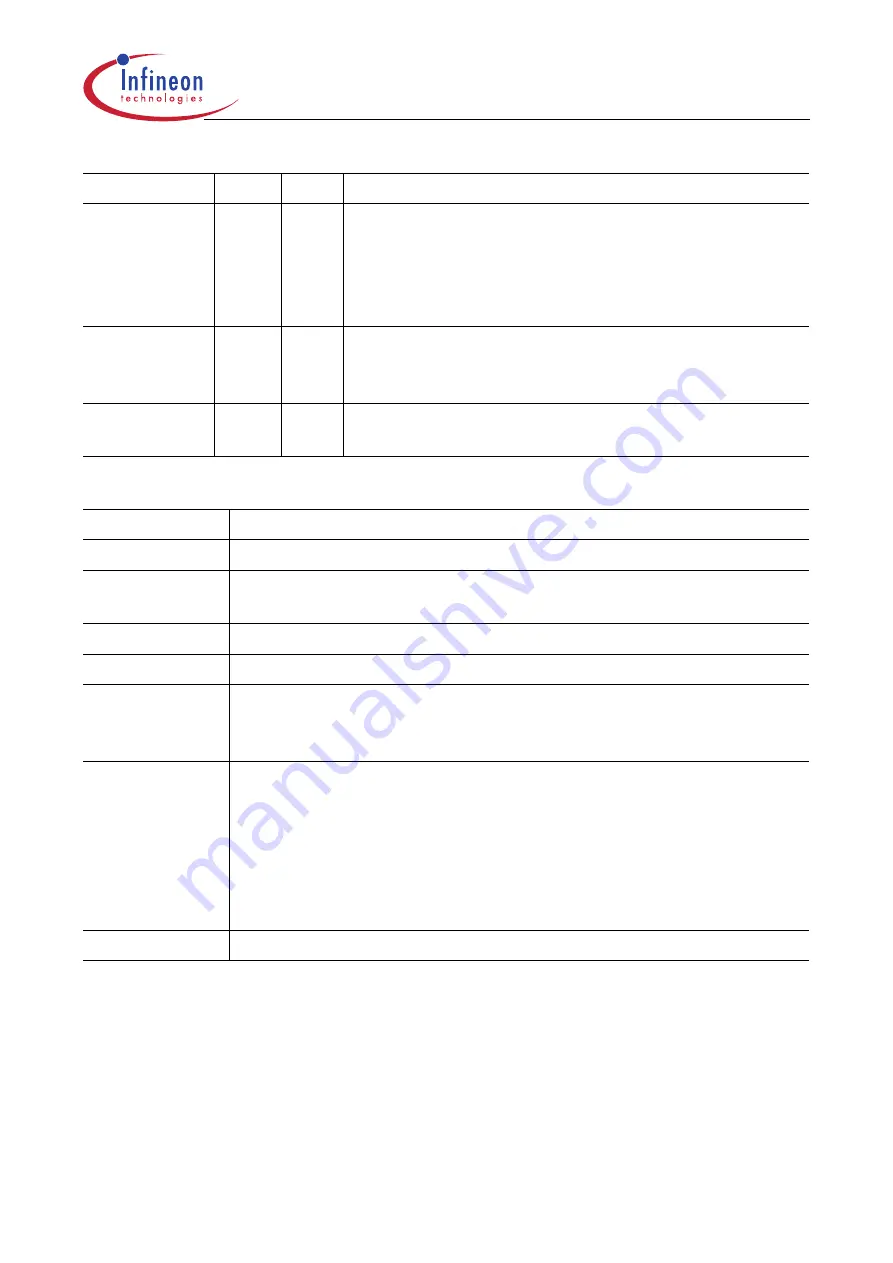

EWRN

6

rh

Error Warning Status

0

No warning limit exceeded.

1

One of the error counters in the Error

Management Logic reached the error warning

limit of 96.

BOFF

7

rh

Bus-Off Status

0

CAN controller is not in the bus-off state.

1

CAN controller is in the bus-off state.

0

5,

[15:8]

r

Reserved; returns ‘0’ if read; should be written with ‘0’.

Table 21-7

Meaning of the LEC Bitfield

LEC Error

Description

No Error

The latest transfer on the CAN bus has been completed successfully.

Stuff Error

More than 5 equal bits in a sequence have occurred in a part of a

received message where this is not allowed.

Form Error

A fixed format part of a received frame has the wrong format.

Ack Error

The transmitted message was not acknowledged by another node.

Bit1 Error

During a message transmission, the CAN node tried to send a

recessive level (‘1’), but the monitored bus value was dominant

(outside the arbitration field and the acknowledge slot).

Bit0 Error

Two different conditions are signaled by this code:

1. During transmission of a message (or acknowledge bit, active

error flag, overload flag), the CAN node tried to send a dominant

level (‘0’), but the monitored bus value has been recessive.

2. During bus-off recovery, this code is set each time a sequence of

11 recessive bits has been monitored. The CPU may use this

code as an indication, that the bus is not continuously disturbed.

CRC Error

The CRC checksum of the received message was incorrect.

Field

Bits

Type

Description