XC161 Derivatives

Peripheral Units (Vol. 2 of 2)

TwinCAN Module

User’s Manual

21-46

V2.2, 2004-01

TwinCAN_X1, V2.1

21.1.10

Module Clock Requirements

The functionality of the TwinCAN module is programmable in several respects. In order

to operate at a specific baudrate with a given functionality a certain minimum module

clock frequency is required.

lists some examples for certain configurations.

These examples cover the worst case conditions where the CPU executes accesses to

the TwinCAN module consecutively and with maximum speed.

The module clock frequency can be reduced (see last column of

) if no frames

without data (data frames with DLC = 0 or remote frames) are transferred over the CAN

bus. This is possible, because internal operations can be executed while the data part is

transferred.

Note: The given numbers are required for the maximum CAN bus speed of 1 Mbit/s. For

lower bit-rates the minimum module clock frequency can be reduced linearly, i.e.

half the frequency is required for a bit-rate of 500 kbit/s.

However, if two nodes are operated with different bit-rates, the module clock

frequency must be chosen according to the fastest node.

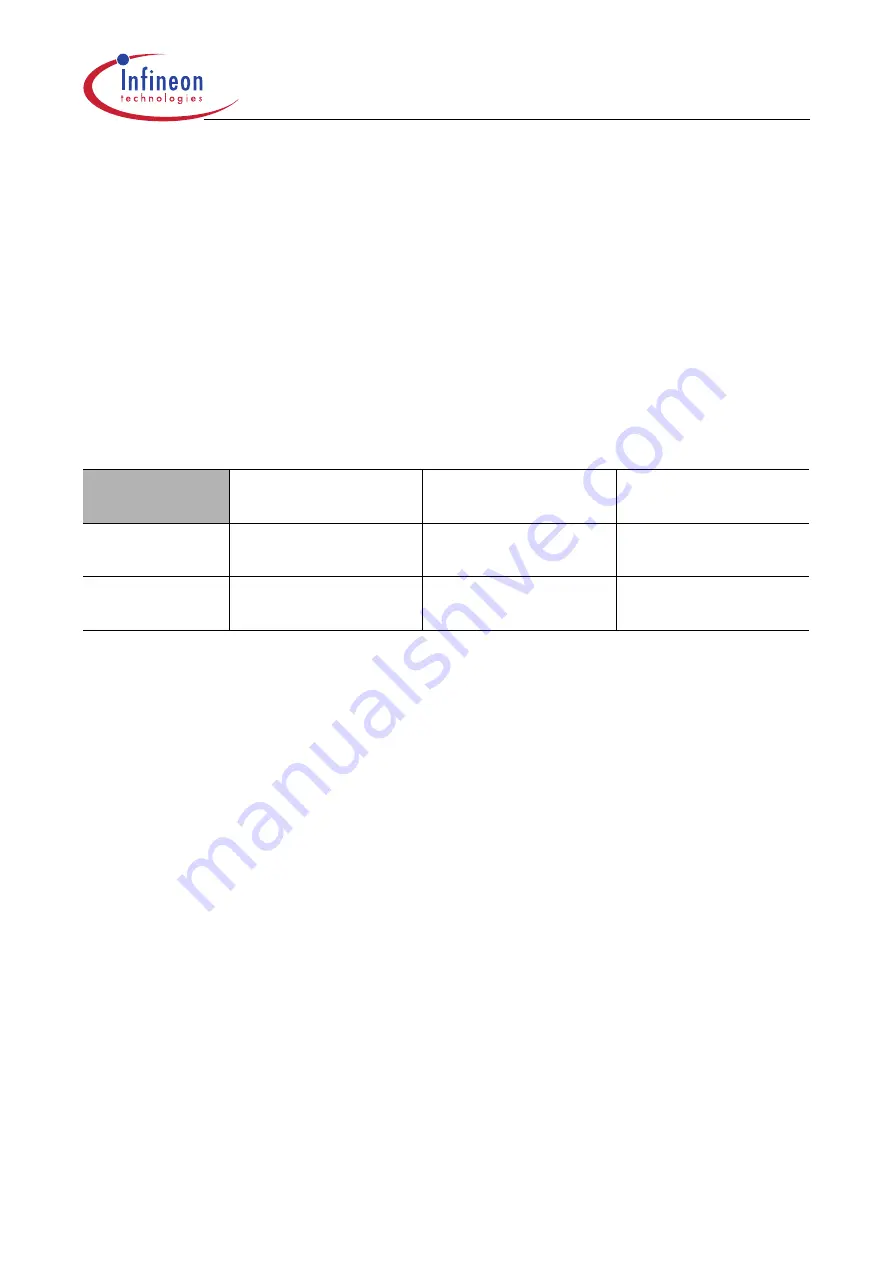

Table 21-6

Minimum Module Clock Frequencies for 1 Mbit/s

1 Node Active,

DLC

≥

0

2 Nodes Active,

DLC

≥

0

2 Nodes Active,

DLC

≥

1

FIFO/gateway

enabled

21 MHz

36 MHz

32 MHz

No

FIFO/gateway

20 MHz

29 MHz

26 MHz