XC161 Derivatives

Peripheral Units (Vol. 2 of 2)

TwinCAN Module

User’s Manual

21-3

V2.2, 2004-01

TwinCAN_X1, V2.1

•

Two separate CAN nodes, subdivided into a bit stream processor, a bit timing control

unit, an error handling logic, an interrupt request generation unit and a node control

logic:

– The bit stream processor performs data, remote, error and overload frames

according to the ISO-DIS 11898 standard. The serial data flow between the CAN

bus line, the input/output shift register and the CRC register is controlled as well

as the parallel data flow between the I/O shift register and the message buffer unit.

– The bit timing control unit defines the sampling point in respect to propagation time

delays and phase shift errors and performs the resynchronization.

– The error handling control logic manages the receive and the transmit error

counter. According the contents in both timers, the CAN controller is set into an

error-active, error-passive or bus-off state.

– The interrupt request generation unit signals globally the successful end of a

message transmit or receive operation, all kinds of transfer problems like bit

stuffing errors, format, acknowledge, CRC or bit state errors, every change of the

CAN bus warning level or of the bus-off state.

– The node control logic enables and disables the node specific interrupt sources,

enters the CAN analyzer mode and administrates a global frame counter.

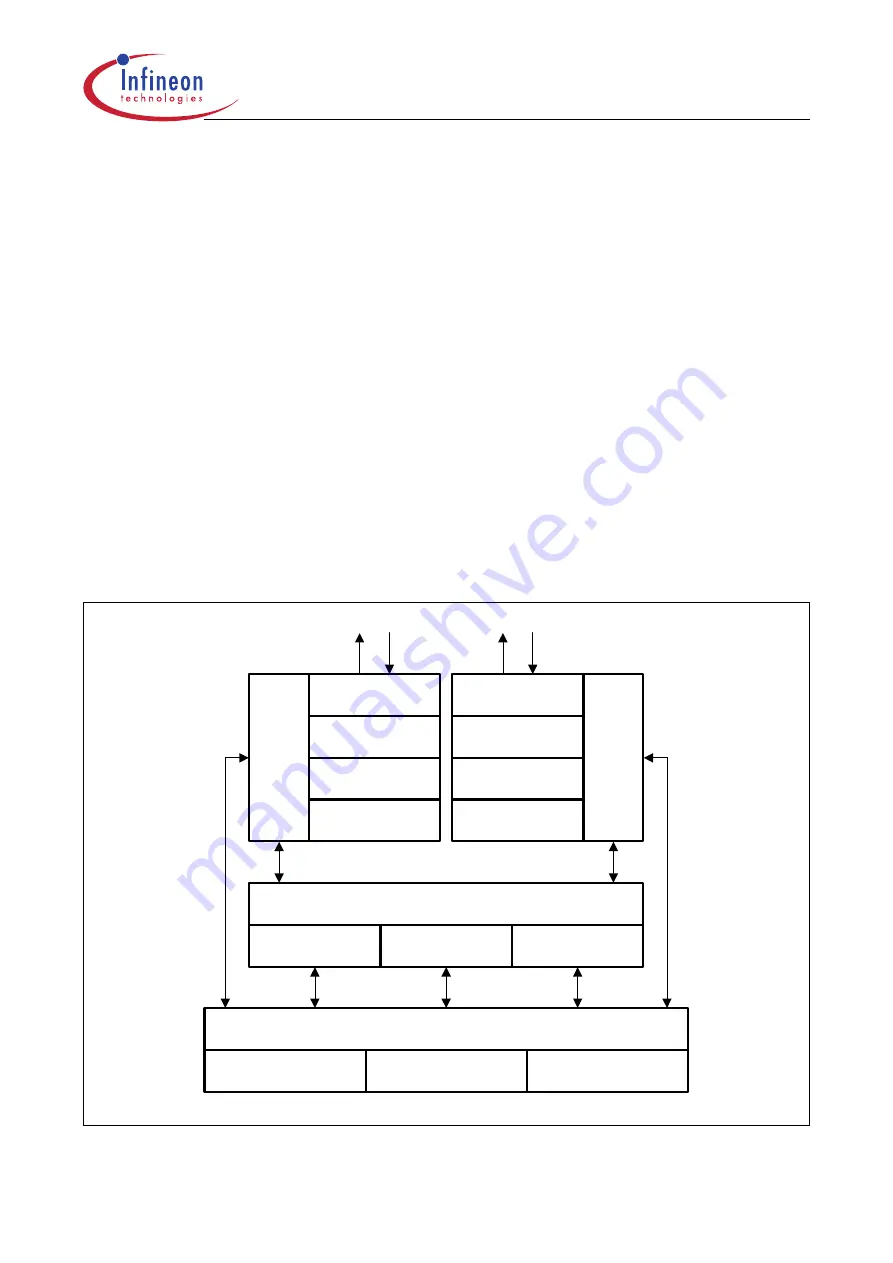

Figure 21-2

Detailed Block Diagram of the TwinCAN Kernel

MCB05472

Interrupt Request

Compressor

Global Status and

Control Logic

Initialization Logic

TwinCAN Conrtol

FIFO Control

Interrupt Request

Generation

Gateway Control

Message Object Buffers

Interrupt Request

Generation

Node A

Control

Logic

Error Handling

Bit Timing Control

Bit Stream

Processor

To CAN Bus A

Interrupt Request

Generation

Error Handling

Bit Timing Control

Bit Stream

Processor

To CAN Bus B

Node B

Control

Logic