MB95630H Series

302

FUJITSU SEMICONDUCTOR LIMITED

MN702-00009-1v0-E

CHAPTER 17 CLOCK SUPERVISOR COUNTER

17.5 Notes on Using Clock Supervisor

Counter

17.5

Notes on Using Clock Supervisor Counter

This section provides notes on using the clock supervisor counter.

■

Notes on Using Clock Supervisor Counter

●

Restrictions

•

The clock supervisor counter must operate in main CR clock mode with the hardware

watchdog timer (running in standby mode). Otherwise, it cannot detect the abnormal state

of the external clock correctly and will hang up if the external clock stops. See "CHAPTER

8 HARDWARE/SOFTWARE WATCHDOG TIMER" for the hardware watchdog timer

(running in standby mode).

•

Use main CR clock mode only. Do not use any other clock mode.

•

If the time-base timer stops, the internal counter stops working. Do not clear the time-base

timer while the clock supervisor counter is counting with the external clock.

•

Select a time-base timer interval that is sufficiently long for the clock supervisor counter to

operate. See Table 17.3-1 for time-base timer intervals.

•

Read the CMDR register when CMCEN = 0. (The value of CMDR remains "0b00000000"

while the clock supervisor counter is operating (CMCEN = 1).)

•

When using the clock supervisor counter, ensure that the machine clock cycle is shorter

than half the time-base timer interval selected. If the machine clock cycle is longer than half

the time-base timer interval selected, CMCEN may remain "1" even after the clock

supervisor counter stops.

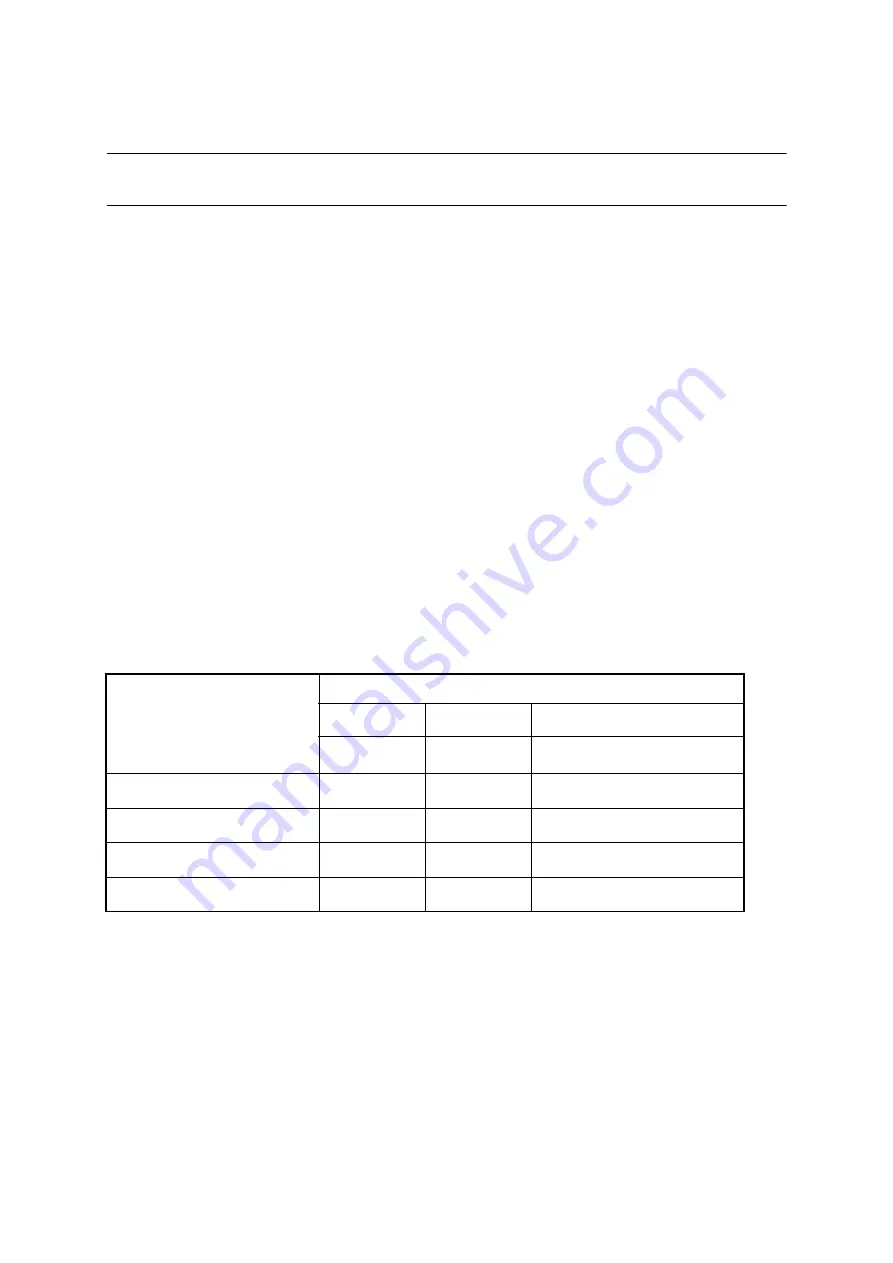

Table 17.5-1 below shows the appropriate clock gear setting for each TBTSEL setting.

❍

: Recommended

x

: Prohibited

Table 17.5-1 Appropriate Clock Gear Setting for Respective TBTSEL Settings

DIV[1:0]

(clock gear setting)

TBTSEL[2:0]

000

001

010 to 111

2

3

×

1/F

CRH

2

5

×

1/F

CRH

2

7

×

1/F

CRH

to 2

17

×

1/F

CRH

00 (1

×

1/F

CRH

)

❍

❍

❍

01 (4

×

1/F

CRH

)

x

❍

❍

10 (8

×

1/F

CRH

)

x

❍

❍

11 (16

×

1/F

CRH

)

x

x

❍