MB95630H Series

208

FUJITSU SEMICONDUCTOR LIMITED

MN702-00009-1v0-E

CHAPTER 14 LIN-UART

14.4 Interrupts

■

LIN Synch Field Edge Detection Interrupt (8/16-bit Composite Timer Interrupt)

Table 14.4-3 shows the control bits and interrupt sources of the LIN synch field edge detection

interrupt.

●

LIN synch field edge detection interrupt (8/16-bit composite timer interrupt)

In operating mode 3, the LIN synch field edge detection interrupt functions when the LIN-

UART performs LIN slave operation.

After a LIN synch break is detected, the internal signal (LSYN) is set to "1" at the first falling

edge of the LIN synch field, and set to "0" after the fifth falling edge. Between both falling

edges, a 8/16-bit composite timer interrupt is generated, provided that the 8/16-bit composite

timer has been configured to receive internal signals and detect rising edges and falling edges

and the 8/16-bit composite interrupt has been enabled.

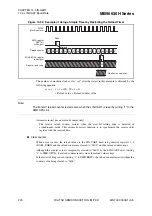

The difference in the count values detected by the 8/16-bit composite timer (see Figure 14.4-1)

is equivalent to eight bits of the master serial clock. A new baud rate can be calculated from

this value. After set, a new baud rate becomes effective from the falling edge detected at the

next start bit set.

Figure 14.4-1 Baud Rate Calculation by 8/16-bit Composite Timer

Table 14.4-3 Interrupt Control Bits and Interrupt Sources of LIN Synch Field Edge Detection

Interrupt

Interrupt

request flag

bit

Flag

register

Operating mode

Interrupt source

Interrupt source

enable bit

Interrupt request flag

clear

0

1

2

3

IR

Tn0CR1

×

×

×

❍

First falling edge of the LIN

synch field

Tn0CR1:IE

Write "0" to Tn0CR1:IR

IR

Tn0CR1

×

×

×

❍

Fifth falling edge of the LIN

synch field

❍

: Bit to be used

×

: Unused bit

LIN

s

ynch field

S

top

b

it

RDR

b

it0

RDR

b

it1

RDR

b

it2

RDR

b

it

3

RDR

b

it4

RDR

b

it5

RDR

b

it6

Reception d

a

t

a

D

a

t

a

= 0x55

Intern

a

l

s

ign

a

l

(L

S

YN)

8

/16-

b

it

compo

s

ite timer

C

a

pt

u

re v

a

l

u

e 1

C

a

pt

u

re v

a

l

u

e 2

Difference in co

u

nt v

a

l

u

e

s

= C

a

pt

u

re v

a

l

u

e 2 - C

a

pt

u

re V

a

l

u

e 1

RDR

b

it7

S

t

a

rt

b

it