MB95630H Series

250

FUJITSU SEMICONDUCTOR LIMITED

MN702-00009-1v0-E

CHAPTER 14 LIN-UART

14.7 Registers

14.7.4

LIN-UART Receive Data Register/LIN-UART

Transmit Data Register (RDR/TDR)

The LIN-UART receive data register and the LIN-UART transmit data register are

located at the same address. If read, they function as the receive data register;

if written, they function as the transmit data register.

■

Register Configuration

■

Register Functions

■

LIN-UART Receive Data Register (RDR)

The LIN-UART receive data register (RDR) is the data buffer register for serial data reception.

Serial input data signals transmitted to the serial input pin (SIN) are converted by the shift register, and the

converted data is stored in the LIN-UART receive data register (RDR).

If the data length is 7 bits, the MSB (RDR:D7) is "0".

The receive data register full flag bit (SSR:RDRF) is set to "1" when received data is stored in the LIN-

UART receive data register (RDR). If the receive interrupt has been enabled (SSR:RIE = 1), a receive

interrupt request is made.

Read the LIN-UART receive data register (RDR) with the receive data register full flag bit (SSR:RDRF)

being "1". The receive data register full flag bit (SSR:RDRF) is automatically cleared to "0" if the LIN-

UART receive data register (RDR) is read. In addition, the receive interrupt is cleared when the receive

interrupt has been enabled and no errors occur.

When a reception error occurs (any of SSR:PE, ORE, or FRE is "1"), the data in the LIN-UART receive data

register (RDR) becomes invalid.

■

LIN-UART Transmit Data Register (TDR)

The LIN-UART transmit data register (TDR) is the data buffer register for serial data transmission.

If the data to be transmitted is written to the LIN-UART transmit data register (TDR) when transmission has

been enabled (SCR:TXE = 1), the transmit data is transferred to the transmit shift register to convert to serial

data, and the serial data is output from the serial data output pin (SOT).

If the data length is 7 bits, the data in the MSB (TDR:D7) is invalid.

The transmit data register empty flag bit (SSR:TDRE) is cleared to "0" when transmit data is written to the

LIN-UART transmit data register (TDR).

The transmit data register empty flag bit (SSR:TDRE) is set to "1" after the data is transferred to the transmit

shift register and data transmission starts.

If the transmit data register empty flag bit (SSR:TDRE) is "1", the next transmit data can be written to TDR.

If the transmit interrupt has been enabled, a transmit interrupt is generated. Write the next transmit data to

TDR after a transmit interrupt or when the transmit data register empty flag bit (SSR:TDRE) is "1".

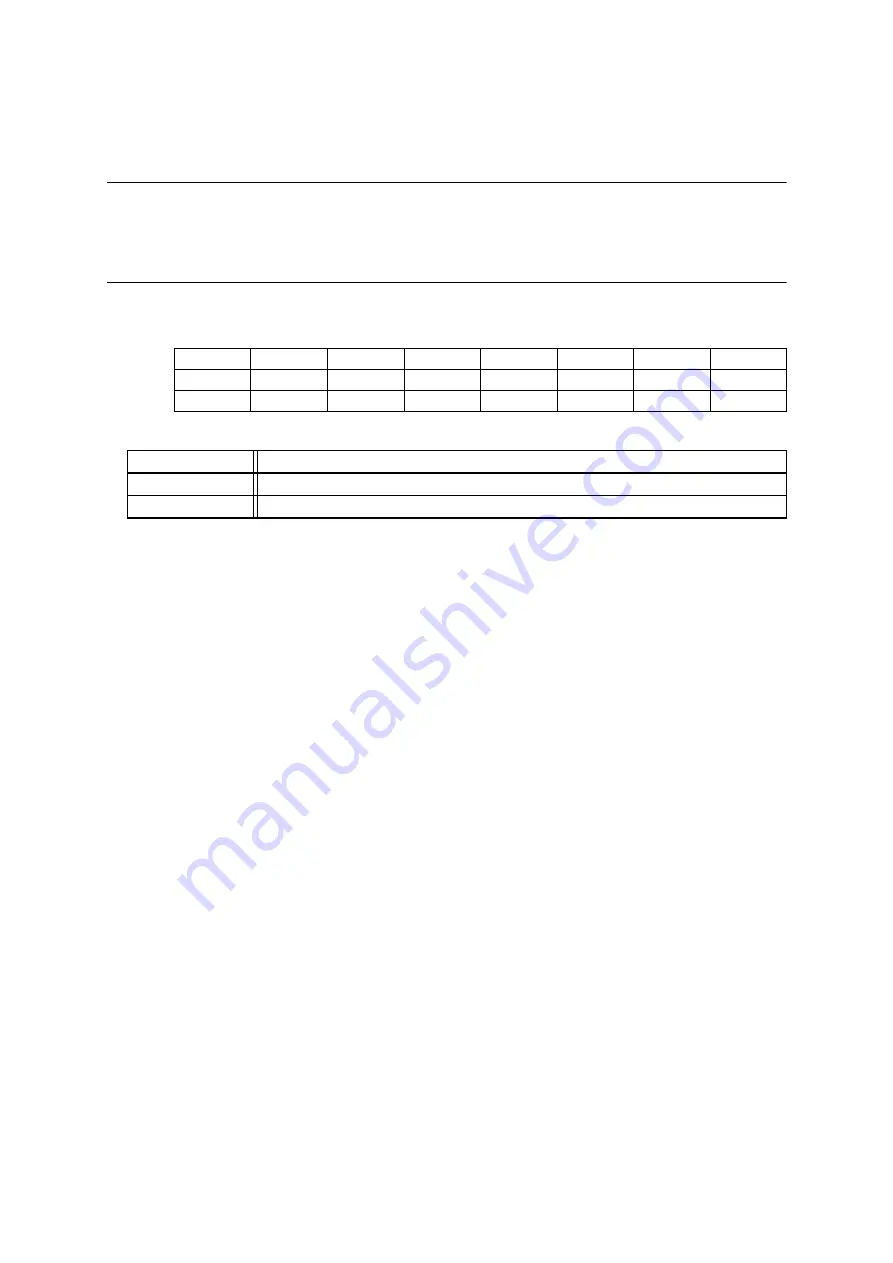

bit

7

6

5

4

3

2

1

0

Field

D7

D6

D5

D4

D3

D2

D1

D0

Attribute

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial value

0

0

0

0

0

0

0

0

Details

Read access:

Reads data from the LIN-UART receive data register.

Write access:

Writes data to the LIN-UART transmit data register.