MB95630H Series

MN702-00009-1v0-E

FUJITSU SEMICONDUCTOR LIMITED

113

CHAPTER 9 WATCH PRESCALER

9.2 Configuration

9.2

Configuration

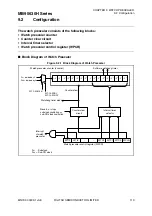

The watch prescaler consists of the following blocks:

• Watch prescaler counter

• Counter clear circuit

• Interval timer selector

• Watch prescaler control register (WPCR)

■

Block Diagram of Watch Prescaler

Figure 9.2-1 Block Diagram of Watch Prescaler

Co

u

nter cle

a

r

circ

u

it

Interv

a

l timer

s

elector

WTIF

WTIE

-

-

WTC1

WTC0

WCLR

W

a

tch pre

s

c

a

ler co

u

nter (co

u

nter)

W

a

tch pre

s

c

a

ler control regi

s

ter (WPCR)

Re

s

et

s

, or

s

top

s

sub

clock o

s

cill

a

tion or

sub

-CR clock o

s

cill

a

tion

Interr

u

pt

of w

a

tch

pre

s

c

a

ler

W

a

tchdog timer cle

a

r

F

CL

divided

b

y 2

F

CRL

divided

b

y 2

F

CL

:

Sub

clock

F

CRL

:

Sub

-CR clock

Co

u

nter cle

a

r

S

oftw

a

re w

a

tchdog timer

WTC2

S

YCC:

S

CM[2:0]

S

YCC2:

S

RDY,

S

YCC2:

S

CRDY

×

2

1

×

2

2

×

2

3

×

2

4

×

2

5

×

2

6

×

2

7

×

2

8

×

2

9

×

2

10

×

2

11

×

2

12

×

2

1

3

×

2

14

×

2

15

×

2

16

×

2

17