MB95630H Series

MN702-00009-1v0-E

FUJITSU SEMICONDUCTOR LIMITED

225

CHAPTER 14 LIN-UART

14.6 Operations of LIN-UART and LIN-UART

Setting Procedure Example

●

Transmission

If the transmit data register empty flag bit (TDRE) in the LIN-UART serial status register

(SSR) is "1", transmit data can be written to the LIN-UART transmit data register (TDR).

Writing data sets the TDRE bit to "0". If transmission has been enabled (SCR:TXE = 1) when

the TDRE bit is set to "0", the data written to TDR is written to the transmit shift register, and,

in the next serial clock cycle, the transmission of the data is started from the start bit.

With the transmit interrupt having been enabled (TIE = 1), if transmit data is transferred from

the LIN-UART transmit data register (TDR) to the transmit shift register, the TDRE bit is set

to "1" and an interrupt is generated.

When the data length is set to 7 bits (CL = 0), bit7 in the TDR register becomes an unused bit

regardless of the transfer direction select bit (BDS) setting (LSB-first or MSB-first).

Note:

Since the initial value of the transmit data register empty flag bit (SSR:TDRE) is "1", an

interrupt is generated immediately when the transmit interrupt is enabled (SSR:TIE = 1).

●

Reception

The reception is performed when reception is enabled (SCR:RXE = 1). When a start bit is

detected, one frame data is received according to the data format defined in the LIN-UART

serial control register (SCR). If an error occurs, an error flag (SSR:PE, ORE, FRE) is set. After

the reception of one frame data ends, the received data is transferred from the receive shift

register to the LIN-UART receive data register (RDR), and the receive data register full flag bit

(SSR:RDRF) is set to "1". If the reception interrupt request has already been enabled (SSR:RIE

= 1) at that time, a reception interrupt request is output.

To read the received data, first check the error flag status to ensure that reception has been

executed normally, then read the data from the LIN-UART receive data register (RDR) if the

reception is normal. If a reception error has occurred, perform error processing.

When the received data is read, the receive data register full flag bit (SSR:RDRF) is cleared.

When the data length is set to 7 bits (CL = 0), bit7 in the TDR register becomes an unused bit

regardless of the transfer direction select bit (BDS) setting (LSB-first or MSB-first).

Note:

Data in the LIN-UART receive data register (RDR) becomes valid, provided that the

receive data register full flag bit (SSR:RDRF) is set to "1" and no error has occurred

(SSR:PE, ORE, FRE = 0).

●

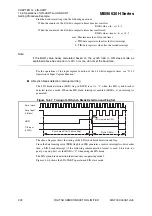

Input clock

Use the internal clock or the external clock. For the baud rate, select the baud rate generator

(SMR:EXT = 0 or 1, OTO = 0).