MB95630H Series

214

FUJITSU SEMICONDUCTOR LIMITED

MN702-00009-1v0-E

CHAPTER 14 LIN-UART

14.5 LIN-UART Baud Rate

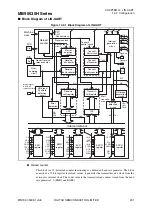

Figure 14.5-1 LIN-UART Baud Rate Selection Circuit

EXT

RE

S

T

BGR7

BGR10

BGR9

BGR

8

BGR6

BGR5

BGR4

BGR

3

BGR2

BGR1

BGR0

Txc = 0?

Txc = v/2?

OTO

1

0

1

0

BGR1

3

BGR12

BGR11

BGR14

F/F

Rxc = 0?

Rxc = v/2?

F/F

EXT

OTO

1

0

Relo

a

d v

a

l

u

e: v

Receive

15-

b

it relo

a

d co

u

nter

Tr

a

n

s

mit

15-

b

it relo

a

d co

u

nter

Relo

a

d v

a

l

u

e: v

Co

u

nter v

a

l

u

e: T

XC

Relo

a

d

RE

S

T

S

t

a

rt

b

it f

a

lling

edge detection

Receive

clock

Tr

a

n

s

mit

clock

S

CK

(Extern

a

l clock

inp

u

t)

Re

s

et

Re

s

et

S

et

S

et

Intern

a

l d

a

t

a

bus

S

MR

regi

s

ter

BGR1

regi

s

ter

BGR0

regi

s

ter

MCLK

(M

a

chine clock)

Relo

a

d