ADSP-2126x SHARC Processor Hardware Reference

A-97

Registers Reference

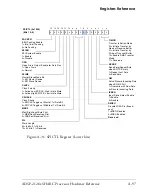

Figure A-31. SPICTL Register (Lower bits)

15 14

13 12 11 10

8

7

6

5

4

3

2

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

PACKEN

TIMOD

Transfer Initiation Mode

00=Initiate Transfer by

Read of Receive Buffer

01=Initiate Transfer by

Write of Transmit Buffer

10=Enable DMA Transfer

Mode

11=Reserved

Reserved

8-Bit Packing Enable

1=8 to 16-bit Packing

0=No Packing

SPIEN

SPI System Enable

1=Enable

0=Disable

OPD

Open Drain Output Enable for Data Pins

1=Open Drain

0=Normal

SPIMS

Master Slave Mode Bit

1=SPI Master Device

0=SPI Slave Device

CLKPL

Clock Polarity

1=Active-Low SPICLK, High in Idle State

0=Active-High SPICLK, Low in Idle State

CPHASE

Clock Phase

1=SPICLK Toggles at Start of 1st Data Bit

0=SPICLK Toggles at Middle of 1st Data Bit

MSBF

Most Significant Byte First

1=MSB Sent/Received First

0=LSB Sent/Received First

SENDZ

Send Zero/Repeat Byte

when SPITX Empty

1=Repeat Last Data

0=Send Zero

GM

Fetch/Discard Incoming Data

when SPIRX Full

1=Overwrite with New Data

0=Discard Incoming Data

ISSEN

Input Slave Select Enable

1=Enable

0=Disable

DMISO

Disable MISO Pin (Broad-

cast)

1=MISO Disabled

0=MISO Enabled

WL

Word Length

00=8 bits, 01=16 bits,

10=32 bits, 11=Reserved

9

SPICTL (0x1000)

(Bits 15–0)

Summary of Contents for ADSP-21261 SHARC

Page 30: ...Contents xxx ADSP 2126x SHARC Processor Hardware Reference ...

Page 40: ...Register Diagram Conventions xl ADSP 2126x SHARC Processor Hardware Reference ...

Page 58: ...Differences From Previous SHARCs 1 18 ADSP 2126x SHARC Processor Hardware Reference ...

Page 112: ...Secondary Processing Element PEy 2 54 ADSP 2126x SHARC Processor Hardware Reference ...

Page 178: ...Summary 3 66 ADSP 2126x SHARC Processor Hardware Reference ...

Page 204: ...DAG Instruction Summary 4 26 ADSP 2126x SHARC Processor Hardware Reference ...

Page 322: ...Setting Up DMA 7 32 ADSP 2126x SHARC Processor Hardware Reference ...

Page 436: ...SPORT Programming Examples 9 86 ADSP 2126x SHARC Processor Hardware Reference ...

Page 521: ...ADSP 2126x SHARC Processor Hardware Reference 11 31 Input Data Port rts IDP_ISR end ...

Page 522: ...Input Data Port Programming Example 11 32 ADSP 2126x SHARC Processor Hardware Reference ...

Page 590: ...Timer Programming Examples 14 20 ADSP 2126x SHARC Processor Hardware Reference ...

Page 796: ...I O Processor Registers A 174 ADSP 2126x SHARC Processor Hardware Reference ...

Page 800: ...B 4 ADSP 2126x SHARC Processor Core Manual ...

Page 846: ...Index I 36 ADSP 2126x SHARC Processor Hardware Reference ...