ADSP-2126x SHARC Processor Hardware Reference

A-103

Registers Reference

SPI DMA Registers

There are five SPI DMA-specific registers which are described in the fol-

lowing sections.

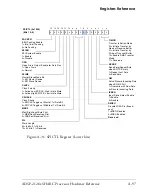

SPI DMA Configuration (SPIDMAC) Register

The SPI DMA Configuration Register contains the control bits for SPI

DMA transfers.

provides the bit descriptions for the

SPIDMAC

register.

The

SPIMME

,

SPIUNF

, and

SPIOVF

bits are sticky; these bits remain set even

if the corresponding

SPISTAT

bits (

MME

,

TUNF

, and

ROVF

) are cleared. To

clear these bits, clear corresponding bits in the

SPISTAT

, register then con-

figure a new DMA

Summary of Contents for ADSP-21261 SHARC

Page 30: ...Contents xxx ADSP 2126x SHARC Processor Hardware Reference ...

Page 40: ...Register Diagram Conventions xl ADSP 2126x SHARC Processor Hardware Reference ...

Page 58: ...Differences From Previous SHARCs 1 18 ADSP 2126x SHARC Processor Hardware Reference ...

Page 112: ...Secondary Processing Element PEy 2 54 ADSP 2126x SHARC Processor Hardware Reference ...

Page 178: ...Summary 3 66 ADSP 2126x SHARC Processor Hardware Reference ...

Page 204: ...DAG Instruction Summary 4 26 ADSP 2126x SHARC Processor Hardware Reference ...

Page 322: ...Setting Up DMA 7 32 ADSP 2126x SHARC Processor Hardware Reference ...

Page 436: ...SPORT Programming Examples 9 86 ADSP 2126x SHARC Processor Hardware Reference ...

Page 521: ...ADSP 2126x SHARC Processor Hardware Reference 11 31 Input Data Port rts IDP_ISR end ...

Page 522: ...Input Data Port Programming Example 11 32 ADSP 2126x SHARC Processor Hardware Reference ...

Page 590: ...Timer Programming Examples 14 20 ADSP 2126x SHARC Processor Hardware Reference ...

Page 796: ...I O Processor Registers A 174 ADSP 2126x SHARC Processor Hardware Reference ...

Page 800: ...B 4 ADSP 2126x SHARC Processor Core Manual ...

Page 846: ...Index I 36 ADSP 2126x SHARC Processor Hardware Reference ...