I/O Processor Registers

A-94

ADSP-2126x SHARC Processor Hardware Reference

The transmit buffer is full after data is written to it and is empty when a

transfer begins and the transmit value loads into the Shift register. The

receive buffer is full at the end of a transfer when the Shift register value is

loaded into the receive buffer. It is empty when the receive buffer is read.

The SPI status also depends on the

PACKEN

bit in the

SPICTL

register. If

packing is enabled, then the receive buffer status is set to full only after

two transfers from the Shift register.

3

TXS

Transmit Data Buffer Status.

Indicates the

TXSPI data buffer status.

0 = Empty

1 = Full

RO

0

4

ROVF

Reception Error (Overflow).

Set when data is

received and the receive buffer is full.

1 = New data received with full RXSPI regis-

ter. See

“Reception Error Bit (ROVF)” on

.

W1C

0

5

RXS

Receive Data Buffer Status.

Indicates the

RXSPI data buffer status.

0 = Empty

1 = Full

RO

0

6

TXCOL

Transmission Collision Error.

The TXCOL

flag is set in the SPISTAT register when a

write to the TXSPI register coincides with the

load of the shift register. See

sion Error Bit (TXCOL)” on page 10-42

W1C

0

31–7

Reserved

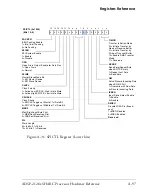

Table A-25. SPISTAT Register Bits (Cont’d)

Bit

Name

Function

Type

Default

Summary of Contents for ADSP-21261 SHARC

Page 30: ...Contents xxx ADSP 2126x SHARC Processor Hardware Reference ...

Page 40: ...Register Diagram Conventions xl ADSP 2126x SHARC Processor Hardware Reference ...

Page 58: ...Differences From Previous SHARCs 1 18 ADSP 2126x SHARC Processor Hardware Reference ...

Page 112: ...Secondary Processing Element PEy 2 54 ADSP 2126x SHARC Processor Hardware Reference ...

Page 178: ...Summary 3 66 ADSP 2126x SHARC Processor Hardware Reference ...

Page 204: ...DAG Instruction Summary 4 26 ADSP 2126x SHARC Processor Hardware Reference ...

Page 322: ...Setting Up DMA 7 32 ADSP 2126x SHARC Processor Hardware Reference ...

Page 436: ...SPORT Programming Examples 9 86 ADSP 2126x SHARC Processor Hardware Reference ...

Page 521: ...ADSP 2126x SHARC Processor Hardware Reference 11 31 Input Data Port rts IDP_ISR end ...

Page 522: ...Input Data Port Programming Example 11 32 ADSP 2126x SHARC Processor Hardware Reference ...

Page 590: ...Timer Programming Examples 14 20 ADSP 2126x SHARC Processor Hardware Reference ...

Page 796: ...I O Processor Registers A 174 ADSP 2126x SHARC Processor Hardware Reference ...

Page 800: ...B 4 ADSP 2126x SHARC Processor Core Manual ...

Page 846: ...Index I 36 ADSP 2126x SHARC Processor Hardware Reference ...