CHAPTER 16 I

2

C BUS

User’s Manual U16896EJ2V0UD

508

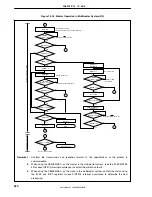

16.10 Extension Code

(1) When the higher 4 bits of the receive address are either 0000 or 1111, the extension code flag (EXC0) is set for

extension code reception and an interrupt request signal (INTIIC0) is issued at the falling edge of the eighth clock.

The local address stored in the SVA0 register is not affected.

(2) If 11110xx0 is set to the SVA0 register by a 10-bit address transfer and 11110xx0 is transferred from the master

device, the results are as follows. Note that the INTIIC0 signal occurs at the falling edge of the eighth clock.

•

Higher 4 bits of data match: IICS0.EXC0 bit = 1

•

7 bits of data match:

IICS0.COI0 bit = 1

(3) Since the processing after the INTIIC0 signal occurs differs according to the data that follows the extension code,

such processing is performed by software.

The slave that has received an extension code is always under communication, even if the addresses mismatch.

For example, when operation as a slave is not desired after the extension code is received, set the IICC0.LREL0

bit to 1 and the CPU will enter the next communication wait state.

Table 16-4. Extension Code Bit Definitions

Slave Address

R/W Bit

Description

0000 000

0

General call address

0000 000

1

Start byte

0000 001

X

CBUS address

0000 010

X

Address that is reserved for different bus format

1111 0xx

X

10-bit slave address specification

<R>

Содержание ?PD703302

Страница 2: ...User s Manual U16896EJ2V0UD 2 MEMO ...