CHAPTER 7 16-BIT TIMER/EVENT COUNTER 0

User’s Manual U16896EJ2V0UD

245

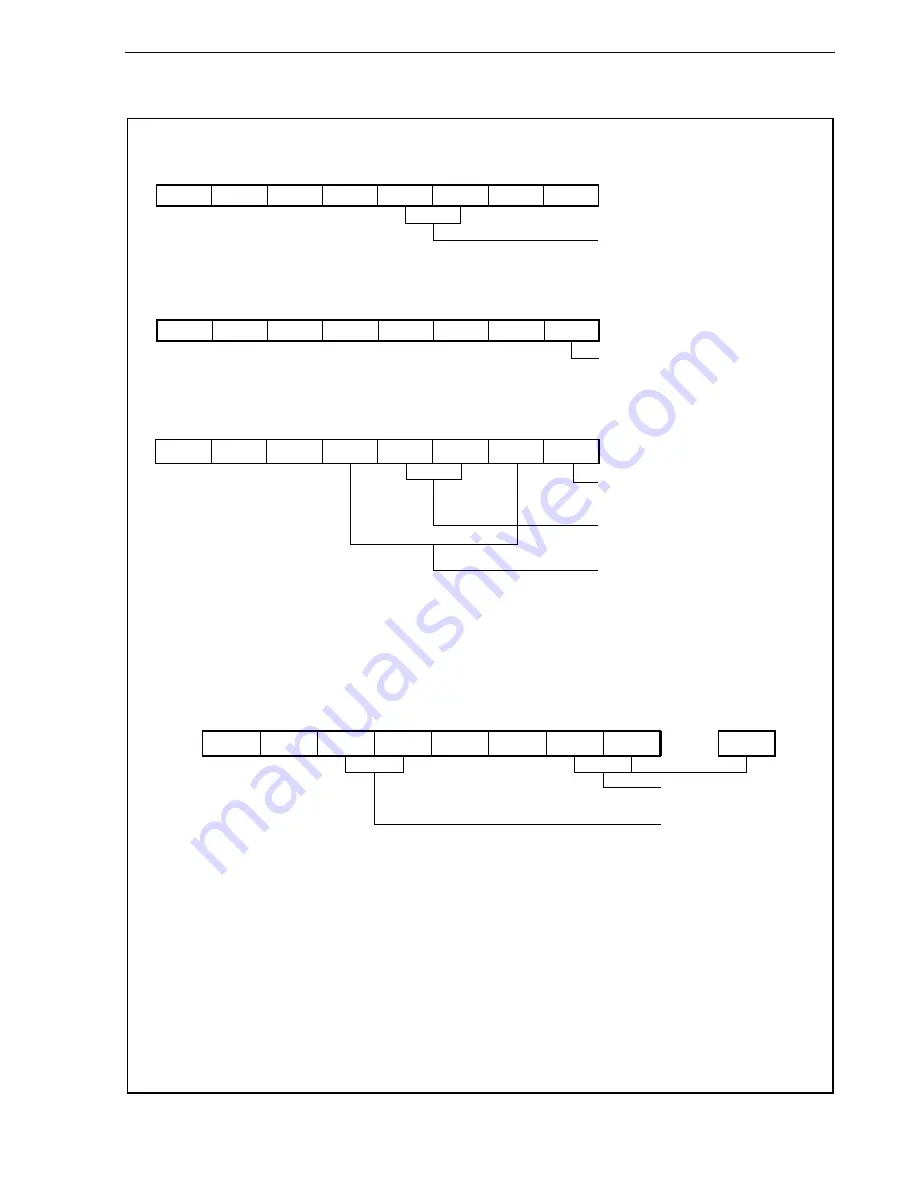

Figure 7-11. Example of Register Settings in External Event Counter Mode

(a) 16-bit timer mode control register 01 (TMC01)

0

0

0

0

1

1

0

0

TMC013 TMC012 TMC011

OVF01

Clears and starts on match

between TM01 and CR010.

(b) Capture/compare control register 01 (CRC01)

0

0

0

0

0

0

0

0

CRC012 CRC011 CRC010

CR010 used as

compare register

(c) 16-bit timer output control register 01 (TOC01)

0

0

0

0/1

0/1

LVR01

LVS01

TOC014

OSPE01

OSPT01

TOC011

TOE01

0: Disables TO01 output.

1: Enables TO01 output.

00: Does not invert TO01 output on match

between TM01 and CR010/CR011.

01: Inverts TO01 output on match between

TM01 and CR010.

10: Inverts TO01 output on match between

TM01 and CR011.

11: Inverts TO01 output on match between

TM01 and CR010/CR011.

Specifies initial value of

TO01 output F/F.

0/1

0/1

0/1

(d) Prescaler mode register 01 (PRM01), selector operation control register 1 (SELCNT1)

0

PRM01

0

0/1

0/1

0

PRM011 PRM010

ISEL11

ES111

ES110

ES101

ES100

Selects count clock

(specifies valid edge of TI010).

00: Falling edge detection

01: Rising edge detection

10: Setting prohibited

11: Both edges detection

0

0

1

1

SELCNT1

(e) 16-bit timer counter 01 (TM01)

By reading the TM01 register, the count value can be read.

(f) 16-bit capture/compare register 010 (CR010)

If M is set to the CR010 register, the interrupt signal (INTTM010) is generated when the number of external

events reaches (M + 1).

Setting the CR010 register to 0000H is prohibited.

(g) 16-bit capture/compare register 011 (CR011)

When this register’s value matches the count value of the TM01 register, an interrupt signal (INTTM011) is

generated. The count value of the TM01 register is not cleared.

Содержание ?PD703302

Страница 2: ...User s Manual U16896EJ2V0UD 2 MEMO ...