CHAPTER 14 ASYNCHRONOUS SERIAL INTERFACE (UART)

User’s Manual U16896EJ2V0UD

429

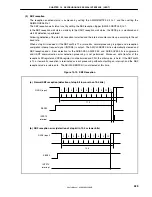

14.6.4 Allowable baud rate range during reception

The degree to which a discrepancy from the transmission destination’s baud rate is allowed during reception is

shown below.

Caution The equations described below should be used to set the baud rate error during reception so

that it always is within the allowable error range.

Figure 14-17. Allowable Baud Rate Range During Reception

FL

1 data frame (11

×

FL)

FLmin

FLmax

UARTn

transfer rate

Latch timing

Start bit

Bit 0

Bit 1

Bit 7

Parity bit

Minimum allowable

transfer rate

Maximum allowable

transfer rate

Stop bit

Start bit

Bit 0

Bit 1

Bit 7

Parity bit

Stop bit

Start bit

Bit 0

Bit 1

Bit 7

Parity bit

Stop bit

As shown in Figure 14-17, after the start bit is detected, the receive data latch timing is determined according

to the counter that was set by the BRGCn register. If all data up to the final data (stop bit) is in time for this

latch timing, the data can be received normally.

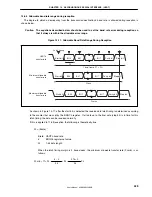

If this is applied to 11-bit reception, the following is theoretically true.

FL = (Brate)

–1

Brate: UARTn baud rate

k:

BRGCn register set value

FL:

1-bit data length

When the latch timing margin is 2 base clocks, the minimum allowable transfer rate (FLmin) is as

follows.

FL

k

2

2

k

21

FL

k

2

2

k

FL

11

min

FL

+

=

×

−

−

×

=

Содержание ?PD703302

Страница 2: ...User s Manual U16896EJ2V0UD 2 MEMO ...