CHAPTER 17 INTERRUPT/EXCEPTION PROCESSING FUNCTION

User’s Manual U16896EJ2V0UD

532

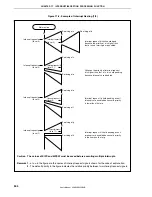

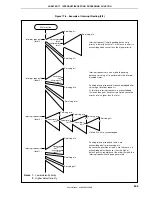

Table 17-1. Interrupt Source List (1/2)

Type Classification

Default

Priority

Name Trigger

Interrupt

Source

Exception

Code

Handler

Address

Restored

PC

Interrupt

Control

Register

RESET pin input

Pin

Reset Interrupt –

RESET

Internal reset input from

WDT1, WDT2

WDT1

WDT2

0000H 00000000H Undefined –

–

NMI

NMI pin valid edge input

Pin

0010H

00000010H nextPC

–

– INTWDT1 WDT1 overflow (when non-

maskable interrupt selected)

WDT1 0020H 00000020H

Note 1

–

Non-

maskable

Interrupt

– INTWDT2 WDT2 overflow (when non-

maskable interrupt selected)

WDT2 0030H 00000030H

Note 1

–

– TRAP0n

Note 2

TRAP

instruction

–

004nH

Note 2

00000040H nextPC

–

Software

exception

Exception

– TRAP1n

Note 2

TRAP

instruction

–

005nH

Note 2

00000050H nextPC

–

Exception

trap

Exception –

ILGOP/

DBG0

Illegal opcode/DBTRAP

instruction

– 0060H

00000060H

nextPC

–

0 INTWDTM1

WDT1 overflow (when interval

timer selected)

WDT1 0080H 00000080H

nextPC WDT1IC

1

INTP0

INTP0 pin valid edge input

Pin

0090H

00000090H nextPC

PIC0

2

INTP1

INTP1 pin valid edge input

Pin

00A0H

000000A0H nextPC

PIC1

3

INTP2

INTP2 pin valid edge input

Pin

00B0H

000000B0H nextPC

PIC2

4

INTP3

INTP3 pin valid edge input

Pin

00C0H

000000C0H nextPC

PIC3

5

INTP4

INTP4 pin valid edge input

Pin

00D0H

000000D0H nextPC

PIC4

6

INTP5

INTP5 pin valid edge input

Pin

00E0H

000000E0H nextPC

PIC5

7

INTP6

INTP6 pin valid edge input

Pin

00F0H

000000F0H nextPC

PIC6

10

INTTM010 TM01 and CR010 match

TM01

0120H

00000120H nextPC

TM0IC10

11

INTTM011 TM01 and CR011 match

TM01

0130H

00000130H nextPC

TM0IC11

12

INTTM50

TM50 and CR50 match

TM50

0140H

00000140H nextPC

TM5IC0

13

INTTM51

TM51 and CR51 match

TM51

0150H

00000150H nextPC

TM5IC1

14

INTCSI00

CSI00 transfer completion

CSI00

0160H

00000160H nextPC

CSI0IC0

15

INTCSI01

CSI01 transfer completion

CSI01

0170H

00000170H nextPC

CSI0IC1

16 INTSRE0 UART0 reception error

occurrence

UART0 0180H 00000180H nextPC SREIC0

17 INTSR0 UART0

reception

completion UART0 0190H 00000190H nextPC SRIC0

18 INTST0

UART0 transmission

completion

UART0 01A0H 000001AH nextPC STIC0

19 INTSRE1 UART1 reception error

occurrence

UART1 01B0H 000001B0H nextPC SREIC1

20 INTSR1 UART1

reception

completion UART1 01C0H 000001C0H

nextPC SRIC1

Maskable Interrupt

21 INTST1

UART1 transmission

completion

UART1 01D0H 000001D0H nextPC STIC1

Notes 1.

For

restoration in the case of INTWDT1 and INTWDT2, refer to

17.10 Cautions

.

2.

n = 0 to FH

Содержание ?PD703302

Страница 2: ...User s Manual U16896EJ2V0UD 2 MEMO ...