CHAPTER 6 16-BIT TIMER/EVENT COUNTER P (TMP)

User’s Manual U16896EJ2V0UD

167

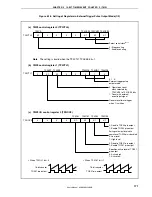

(c) Operation of TP0CCR1 register

Figure 6-13. Configuration of TP0CCR1 Register

CCR0 buffer register

TP0CE bit

TP0CCR0 register

16-bit counter

TP0CCR1 register

CCR1 buffer register

Clear

Match signal

Match signal

INTTP0CC0 signal

INTTP0CC1 signal

Edge

detector

TIP00 pin

If the set value of the TP0CCR1 register is smaller than the set value of the TP0CCR0 register, the

INTTP0CC1 signal is generated once per cycle.

Figure 6-14. Timing Chart When D

01

≥

D

11

FFFFH

16-bit counter

0000H

TP0CE bit

TP0CCR0 register

INTTP0CC0 signal

TP0CCR1 register

INTTP0CC1 signal

D

01

D

11

D

01

D

11

D

11

D

11

D

11

D

01

D

01

D

01

Содержание ?PD703302

Страница 2: ...User s Manual U16896EJ2V0UD 2 MEMO ...