CHAPTER 14 ASYNCHRONOUS SERIAL INTERFACE (UART)

User’s Manual U16896EJ2V0UD

419

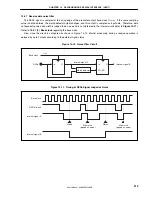

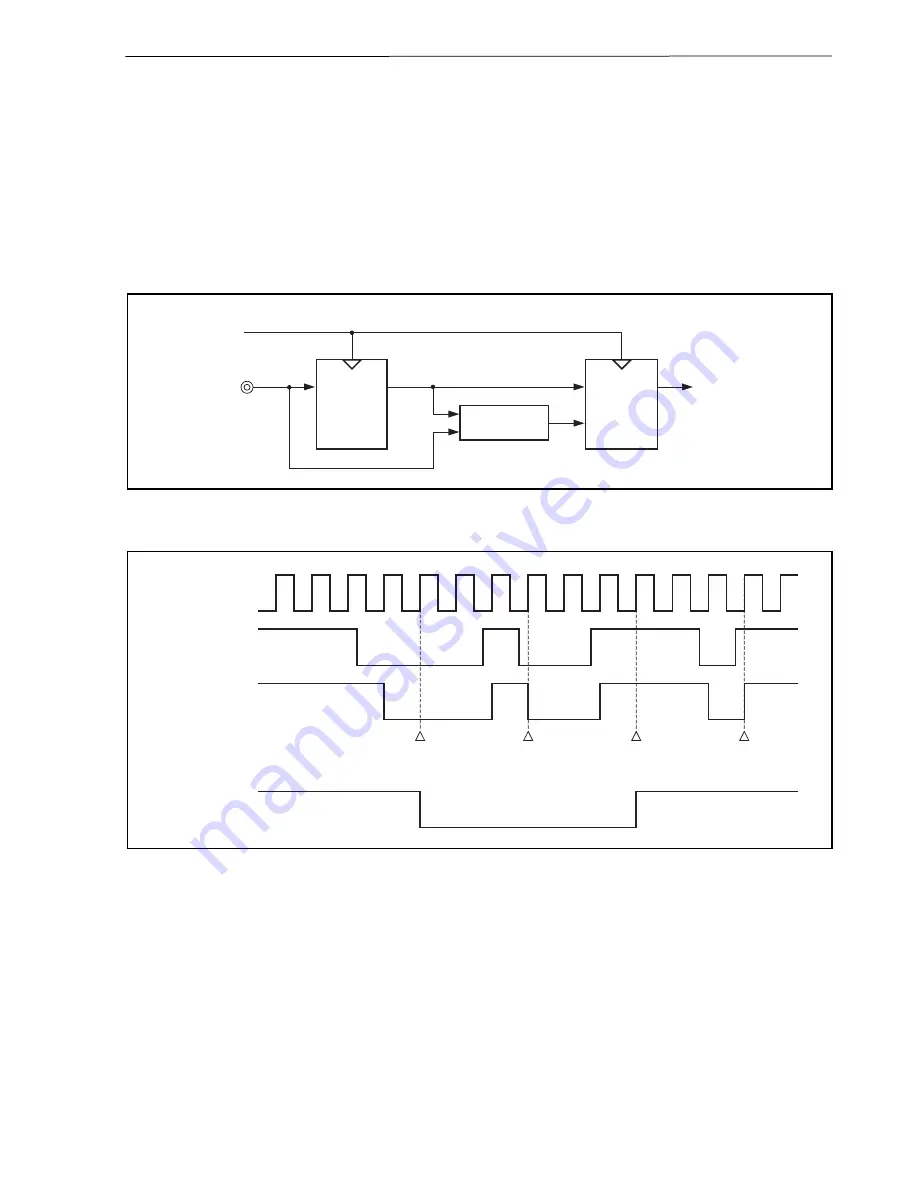

14.5.7 Receive data noise filter

The RXDn signal is sampled at the rising edge of the prescaler output base clock (f

UCLK

). If the same sampling

value is obtained twice, the match detector output changes, and this output is sampled as input data. Therefore, data

not exceeding one clock width is judged to be noise and is not delivered to the internal circuit (refer to

Figure 14-11

).

Refer to

14.6.1 (1) Base clock

regarding the base clock.

Also, since the circuit is configured as shown in Figure 14-10, internal processing during a receive operation is

delayed by up to 2 clocks according to the external signal status.

Figure 14-10. Noise Filter Circuit

RXDn

Q

Base clock

In

LD_EN

Q

In

Internal signal A

Internal signal B

Match detector

f

UCLK

Figure 14-11. Timing of RXDn Signal Judged as Noise

Internal signal A

Base clock

RXDn (input)

Internal signal B

Match

Mismatch

(judged as noise)

Mismatch

(judged as noise)

Match

Содержание ?PD703302

Страница 2: ...User s Manual U16896EJ2V0UD 2 MEMO ...