CHAPTER 7 16-BIT TIMER/EVENT COUNTER 0

User’s Manual U16896EJ2V0UD

255

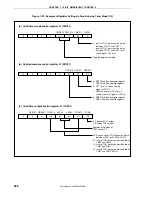

Figure 7-18. Timing Example of Clear & Start Mode Entered by TI010 Pin Valid Edge Input

(CR010 Register: Capture Register, CR011 Register: Compare Register) (2/2)

(b) TOC01 = 13H, PRM01 = 10H, CRC01 = 03H, TMC01 = 0AH, CR011 = 0003H

TM01 register

0000H

Operable bits

(TMC013, TMC012)

Capture & count clear input

(TI010 pin input)

Compare register

(CR010)

Compare match interrupt

(INTTM010)

Capture register

(CR011)

Capture interrupt

(INTTM011)

TO01 pin output

0003H

0003H

10

P

N

M

S

00

4

4

4

4

L

0000H

M

N

S

P

This is an application example where the width set to the CR011 register (4 clocks in this example) is to be

output from the TO01 pin when the count value has been captured & cleared.

The TM01 register is cleared (to 0000H) at the rising edge detection of the TI010 pin and captured to the

CR010 register at the falling edge detection of the TI010 pin. The output level of the TO01 pin is inverted when

the TM01 register is cleared (to 0000H) because the rising edge of the TI010 pin has been detected or when

the value of the TM01 register matches that of a compare register (CR011).

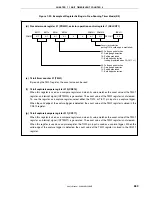

When the CRC01.CRC011 bit is 1, the count value of the TM01 register is captured to the CR010 register in

the phase reverse to that of the input signal of the TI010 pin, but the capture interrupt signal (INTTM010) is not

generated. However, the INTTM010 interrupt is generated when the valid edge of the TI011 pin is detected.

Mask the INTTM010 signal when it is not used.

Содержание ?PD703302

Страница 2: ...User s Manual U16896EJ2V0UD 2 MEMO ...