Rev. 3.0, 03/01, page 344 of 390

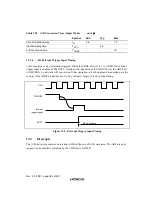

Table 19.4

A/D Conversion Time (Single Mode) unit:

µµµµ

s

Symbol

Min

Typ

Max

Synchronization delay

t

D

0.5

-

1.2

Input sampling time

T

SPL

-

2.8

-

A/D conversion time

T

CONV

-

-

10

19.3.4

A/D External Trigger Input Timing

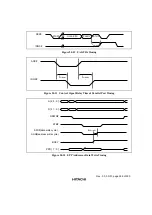

A/D conversion can be externally triggered. When the TRGE bit is set to 1 in ADCR, the external

trigger input is enabled by TMOUT#. A high-to-low transition at the TMOUT# sets the ADST bit

of ADCSR to 1, and starts A/D conversion. Other operation, in both single and scan modes, are the

same as if the ADST bit had been set to 1 by software. Figure 19-5 shows the timing.

CLK

TMOUT#

Internal

trigger signal

ADST

A/D conversion

Figure 19.5 External Trigger Input Timing

19.4

Interrupts

The A/D converter generates an interrupt (ADI) at the end of A/D conversion. The ADI interrupt

request can be enabled or disabled by the ADIE bit in ADCSR.

Содержание HD64465

Страница 25: ...Rev 3 0 03 01 page 6 of 390 ...

Страница 59: ...Rev 3 0 03 01 page 40 of 390 ...

Страница 97: ...Rev 3 0 03 01 page 78 of 390 ...

Страница 147: ...Rev 3 0 03 01 page 128 of 390 ...

Страница 199: ...Rev 3 0 03 01 page 180 of 390 ...

Страница 247: ...Rev 3 0 03 01 page 228 of 390 ...

Страница 385: ...Rev 3 0 03 01 page 366 of 390 ...

Страница 389: ...Rev 3 0 03 01 page 370 of 390 ...

Страница 409: ...Rev 3 0 03 01 page 390 of 390 ...