Rev. 3.0, 03/01, page 359 of 390

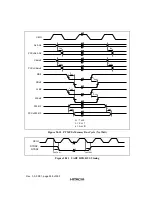

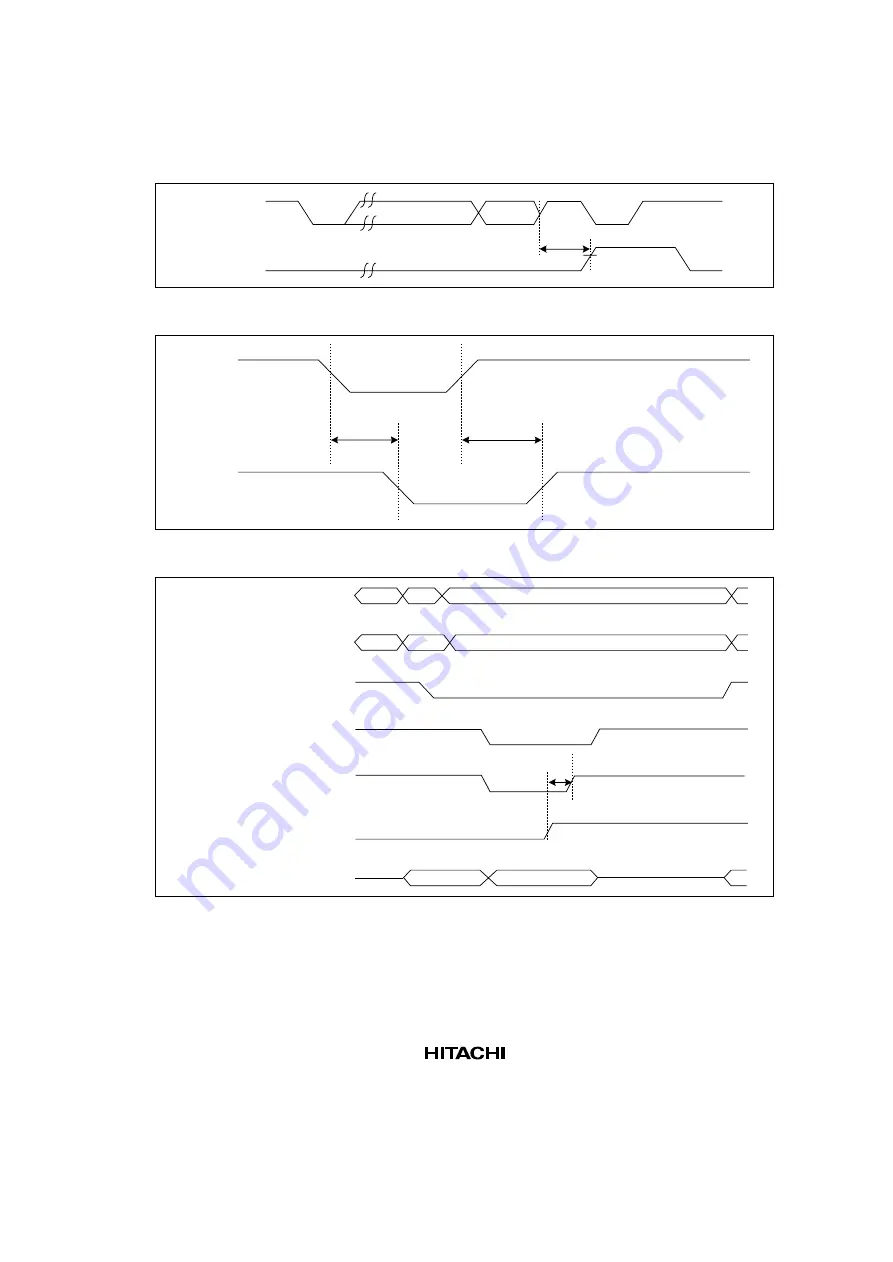

RXD0

START

DATA BITS

PARITY

STOP

IRQ0#

t

URIRQD

Figure 20.12 UART Rx Timing

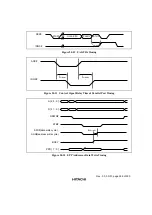

ACK#

IRQ0#

t

PPIRQD1

t

PPIRQD2

Figure 20.13 Control Signal Delay Time of Parallel Port Timing

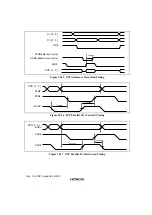

A [ 25 : 0 ]

D [ 31 : 0 ]

RDWR#

STB#

AFD#(data write cycle) ,

SLIN#(address write cycle)

BUSY

PPD [ 7 : 0 ]

t

PPSLIND1

Figure 20.14 EPP Address or Data Write Timing

Содержание HD64465

Страница 25: ...Rev 3 0 03 01 page 6 of 390 ...

Страница 59: ...Rev 3 0 03 01 page 40 of 390 ...

Страница 97: ...Rev 3 0 03 01 page 78 of 390 ...

Страница 147: ...Rev 3 0 03 01 page 128 of 390 ...

Страница 199: ...Rev 3 0 03 01 page 180 of 390 ...

Страница 247: ...Rev 3 0 03 01 page 228 of 390 ...

Страница 385: ...Rev 3 0 03 01 page 366 of 390 ...

Страница 389: ...Rev 3 0 03 01 page 370 of 390 ...

Страница 409: ...Rev 3 0 03 01 page 390 of 390 ...