MOTOROLA CMOS LOGIC DATA

6–37

MC14014B MC14021B

8-Bit Static Shift Register

The MC14014B and MC14021B 8–bit static shift registers are constructed

with MOS P–channel and N–channel enhancement mode devices in a single

monolithic structure. These shift registers find primary use in parallel–to–

serial data conversion, synchronous and asynchronous parallel input, serial

output data queueing; and other general purpose register applications

requiring low power and/or high noise immunity.

•

Synchronous Parallel Input/Serial Output (MC14014B)

•

Asynchronous Parallel Input/Serial Output (MC14021B)

•

Synchronous Serial Input/Serial Output

•

Full Static Operation

•

“Q” Outputs from Sixth, Seventh, and Eighth Stages

•

Double Diode Input Protection

•

Supply Voltage Range = 3.0 Vdc to 18 Vdc

•

Capable of Driving Two Low–power TTL Loads or One Low–power

Schottky TTL Load Over the Rated Temperature Range

•

MC14014B Pin–for–Pin Replacement for CD4014B

•

MC14021B Pin–for–Pin Replacement for CD4021B

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

MAXIMUM RATINGS*

(Voltages Referenced to VSS)

ÎÎÎÎ

ÎÎÎÎ

Symbol

ÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎ

Parameter

ÎÎÎÎÎÎ

ÎÎÎÎÎÎ

Value

ÎÎÎ

ÎÎÎ

Unit

ÎÎÎÎ

ÎÎÎÎ

VDD

ÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎ

DC Supply Voltage

ÎÎÎÎÎÎ

ÎÎÎÎÎÎ

– 0.5 to + 18.0

ÎÎÎ

ÎÎÎ

V

ÎÎÎÎ

ÎÎÎÎ

Vin, Vout

ÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎ

Input or Output Voltage (DC or Transient)

ÎÎÎÎÎÎ

ÎÎÎÎÎÎ

– 0.5 to VDD + 0.5

ÎÎÎ

ÎÎÎ

V

ÎÎÎÎ

ÎÎÎÎ

lin, lout

ÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎ

Input or Output Current (DC or Transient),

per Pin

ÎÎÎÎÎÎ

ÎÎÎÎÎÎ

±

10

ÎÎÎ

ÎÎÎ

mA

ÎÎÎÎ

ÎÎÎÎ

PD

ÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎ

Power Dissipation, per Package†

ÎÎÎÎÎÎ

ÎÎÎÎÎÎ

500

ÎÎÎ

ÎÎÎ

mW

ÎÎÎÎ

ÎÎÎÎ

Tstg

ÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎ

Storage Temperature

ÎÎÎÎÎÎ

ÎÎÎÎÎÎ

– 65 to + 150

ÎÎÎ

ÎÎÎ

_

C

ÎÎÎÎ

ÎÎÎÎ

TL

ÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎ

Lead Temperature (8–Second Soldering)

ÎÎÎÎÎÎ

ÎÎÎÎÎÎ

260

ÎÎÎ

ÎÎÎ

_

C

* Maximum Ratings are those values beyond which damage to the device may occur.

†Temperature Derating:

Plastic “P and D/DW” Packages: – 7.0 mW/

_

C From 65

_

C To 125

_

C

Ceramic “L” Packages: – 12 mW/

_

C From 100

_

C To 125

_

C

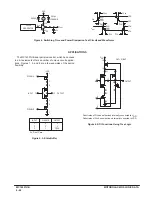

LOGIC DIAGRAM

CLOCK

DS

P/S

P1

P2

P3

P6

P7

P8

7

6

5

14

15

1

10

11

9

D

C

Q

D

C

Q

D

C

Q

D

C

Q

D

C

Q

D

C

Q

Q

Q

2

12

3

Q8

Q7

Q6

VDD = PIN 16

VSS = PIN 8

P4 = PIN 4

P5 = PIN 13

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

MC14014B

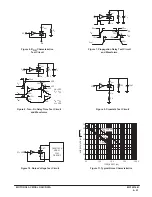

MC14021B

L SUFFIX

CERAMIC

CASE 620

ORDERING INFORMATION

MC14XXXBCP

Plastic

MC14XXXBCL

Ceramic

MC14XXXBD

SOIC

TA = – 55

°

to 125

°

C for all packages.

P SUFFIX

PLASTIC

CASE 648

D SUFFIX

SOIC

CASE 751B

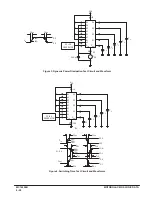

TRUTH TABLE

Q6

Q7

Q8

t

Clock DS P/S t=n+6

t=n+7

t=n+8

n

0

0

0

?

?

n+1

1

0

1

0

?

n+2

0

0

0

1

0

n+3

1

0

1

0

1

X

0

Q6

Q7

Q8

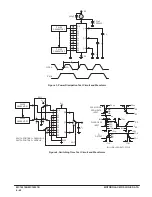

SERIAL OPERATION:

Clock

MC14014B

MC14021B DS

P/S

Pn *Qn

X

X

1

0

0

X

X

1

1

1

* Q6, Q7, & Q8 are available externally

PARALLEL OPERATION:

X = Don’t Care

Summary of Contents for CMOS Logic

Page 1: ......

Page 5: ...iv MOTOROLA CMOS LOGIC DATA ...

Page 6: ...Master Index 1 ...

Page 12: ...Product Selection Guide 2 ...

Page 17: ...The Better Program 3 ...

Page 20: ...B and UB Series Family Data 4 ...

Page 25: ...CMOS Handling and Design Guidelines 5 ...

Page 32: ...CMOS Handling and Design Guidelines 5 ...

Page 39: ...Data Sheets 6 ...

Page 234: ...MOTOROLA CMOS LOGIC DATA MC14174B 6 196 FUNCTIONAL BLOCK DIAGRAM TIMING DIAGRAM ...

Page 238: ...MOTOROLA CMOS LOGIC DATA MC14175B 6 200 FUNCTIONAL BLOCK DIAGRAM TIMING DIAGRAM ...

Page 555: ...CMOS Reliability 7 ...

Page 561: ...Equivalent Gate Count 8 ...

Page 563: ...Packaging Information Including Surface Mounts 9 ...

Page 571: ......