MOTOROLA CMOS LOGIC DATA

6–401

MC14549B MC14559B

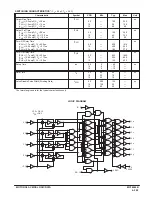

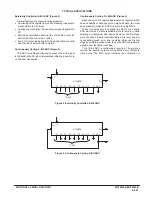

SWITCHING TIME TEST CIRCUIT AND WAVEFORMS

1

fcl

tWH(cl)

50%

50%

tsu

tsu

tsu

tWH(D)

tPHL

tPLH

50%

50%

90%

10%

tTLH

tPLH

tTHL

90%

50%

10%

tTLH

Sout

Q7

D

SC

C

NOTE: Pin 10 = VSS

CL

CL

CL

CL

CL

CL

CL

CL

CL

CL

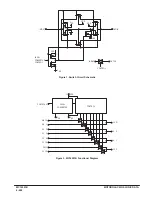

VDD

VSS

Q7

Q6

Q5

Q4

Q3

Q2

Q1

Q0

EOC

Sout

C

SC

FF(MR)

D

PROGRAMMABLE

PULSE

GENERATOR

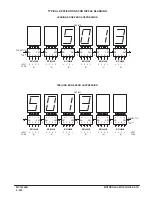

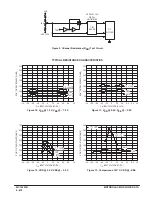

TIMING DIAGRAM

* — Q8 is ninth–bit of serial information available from 8–bit register.

NOTE: Pin 10 = VSS

INH — Indicates Serial Out is inhibited low.

— Don’t care condition

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

CLOCK

SC

D

Q7

Q6

Q5

Q4

Q3

Q2

Q1

Q0

EOC

Sout

INH

INH Q7 Q6

Q7

Q5

Q3

Q1

Q8* INH

Q6

Q4

Q2

Q0

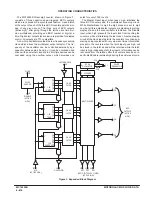

Summary of Contents for CMOS Logic

Page 1: ......

Page 5: ...iv MOTOROLA CMOS LOGIC DATA ...

Page 6: ...Master Index 1 ...

Page 12: ...Product Selection Guide 2 ...

Page 17: ...The Better Program 3 ...

Page 20: ...B and UB Series Family Data 4 ...

Page 25: ...CMOS Handling and Design Guidelines 5 ...

Page 32: ...CMOS Handling and Design Guidelines 5 ...

Page 39: ...Data Sheets 6 ...

Page 234: ...MOTOROLA CMOS LOGIC DATA MC14174B 6 196 FUNCTIONAL BLOCK DIAGRAM TIMING DIAGRAM ...

Page 238: ...MOTOROLA CMOS LOGIC DATA MC14175B 6 200 FUNCTIONAL BLOCK DIAGRAM TIMING DIAGRAM ...

Page 555: ...CMOS Reliability 7 ...

Page 561: ...Equivalent Gate Count 8 ...

Page 563: ...Packaging Information Including Surface Mounts 9 ...

Page 571: ......