MOTOROLA CMOS LOGIC DATA

6–469

MC14568B

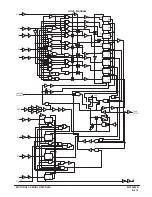

Figure 8. Frequency Synthesizer Using MC14568B, MC14569B and MC14522B

(Without Mixer)

Divide ratio = 160N1 + 16N2 + N3

Example:

fout = N1 (MHz) + N2 (x 100 kHz) + N3 (x25 kHz)

Frequency range = 5 MHz

Channel spacing = 25 kHz

Reference frequency = 6.25 kHz

Figures shown in parenthesis refer to example.

Recommended reading:

(1) AN535: “Phase–Lock Techniques”

(2) AR254: “Phase–Locked Loop Design Articles”

(5 MHz)

(VDD)

VDD

VDD

PCin

C1

CTL

“0”

MC14568B

PCout

G

F

PE

VSS

VDD

DP0 – – – – – DP3

VCO

fout

DP0 – – – – – DP3

C

PE

MC14522B

“0”

Q

ZERO DETECT

(BCD)

BINARY

CF

C

N1

(0 – 5)

(625 kHz STEPS)

N2

(0 – 9)

(62.5 kHz STEPS)

N3

(0, 4, 8, 12)

(6.25 kHz STEPS)

MC14569B

Summary of Contents for CMOS Logic

Page 1: ......

Page 5: ...iv MOTOROLA CMOS LOGIC DATA ...

Page 6: ...Master Index 1 ...

Page 12: ...Product Selection Guide 2 ...

Page 17: ...The Better Program 3 ...

Page 20: ...B and UB Series Family Data 4 ...

Page 25: ...CMOS Handling and Design Guidelines 5 ...

Page 32: ...CMOS Handling and Design Guidelines 5 ...

Page 39: ...Data Sheets 6 ...

Page 234: ...MOTOROLA CMOS LOGIC DATA MC14174B 6 196 FUNCTIONAL BLOCK DIAGRAM TIMING DIAGRAM ...

Page 238: ...MOTOROLA CMOS LOGIC DATA MC14175B 6 200 FUNCTIONAL BLOCK DIAGRAM TIMING DIAGRAM ...

Page 555: ...CMOS Reliability 7 ...

Page 561: ...Equivalent Gate Count 8 ...

Page 563: ...Packaging Information Including Surface Mounts 9 ...

Page 571: ......