MOTOROLA CMOS LOGIC DATA

MC14506UB

6–240

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

SWITCHING CHARACTERISTICS*

(CL = 50 pF, TA = 25

_

C)

Characteristic

Symbol

VDD

Min

Typ #

Max

Unit

Output Rise and Fall Time

tTLH, tTHL = (1.5 ns/pF) CL + 25 ns

tTLH, tTHL = (0.75 ns/pF) CL + 12.5 ns

tTLH, tTHL = (0.55 ns/pF) CL + 9.5 ns

tTLH, tTHL

5.0

10

15

—

—

—

100

50

40

200

100

80

ns

Data Propagation Delay Time

tPLH = (1.7 ns/pF) CL + 210 ns

tPLH = (0.66 ns/pF) CL + 77 ns

tPLH = (0.5 ns/pF) CL + 50 ns

tPLH

5.0

10

15

—

—

—

295

110

75

580

225

180

ns

tPHL = (1.7 ns/pF) CL + 185 ns

tPHL = (0.66 ns/pF) CL + 62 ns

tPHL = (0.5 ns/pF) CL + 40 ns

tPHL

5.0

10

15

—

—

—

270

95

65

480

175

140

ns

Expand Propagation Delay Time

tPLH = (1.7 ns/pF) CL + 95 ns

tPLH = (0.66 ns/pF) CL + 42 ns

tPLH = (0.5 ns/pF) CL + 25 ns

tPLH

5.0

10

15

—

—

—

180

75

50

430

160

125

ns

tPHL = (1.7 ns/pF) CL + 115 ns

tPHL = (0.66 ns/pF) CL + 47 ns

tPHL = (0.5 ns/pF) CL + 30 ns

tPHL

5.0

10

15

—

—

—

200

80

55

330

110

90

ns

Inhibit Propagation Delay Time

tPLH = (1.7 ns/pF) CL + 135 ns

tPLH = (0.66 ns/pF) CL + 67 ns

tPLH = (0.5 ns/pF) CL + 40 ns

tPLH

5.0

10

15

—

—

—

220

100

65

500

225

160

ns

tPHL = (1.7 ns/pF) CL + 145 ns

tPHL = (0.66 ns/pF) CL + 62 ns

tPHL = (0.5 ns/pF) CL + 35 ns

tPHL

5.0

10

15

—

—

—

230

95

60

400

175

150

ns

3–State Propagation Delay Time

“1” to High Impedance

tPHZ

5.0

10

15

—

—

—

60

45

35

150

110

90

ns

“0” to High Impedance

tPLZ

5.0

10

15

—

—

—

90

55

40

225

140

100

ns

High Impedance to “1”

tPZH

5.0

10

15

—

—

—

110

50

40

300

125

100

ns

High Impedance to “0”

tPZL

5.0

10

15

—

—

—

170

70

50

425

175

125

ns

* The formulas given are for the typical characteristics only at 25

_

C.

#Data labelled “Typ” Is not to be used for design purposes but is intended as an indication of the IC’s potential performance.

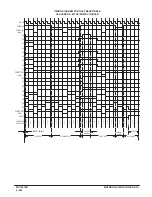

Figure 1. Typical Voltage Transfer Characteristics

(a) Expand Inputs

(b) Data Inputs

16

14

12

10

8.0

6.0

4.0

2.0

0

16

14

12

10

8.0

6.0

4.0

2.0

0

Vin, INPUT VOLTAGE (Vdc)

V

out

, OUTPUT

VOL

TAGE

(Vdc)

a

b

c

c

a

b

a

b

c

VDD = 15 Vdc

10 Vdc

5.0 Vdc

a

b

c

TA = + 125

°

C

TA = + 25

°

C

TA = – 55

°

C

UNUSED INPUTS

CONNECTED TO

VSS

16

14

12

10

8.0

6.0

4.0

2.0

0

16

14

12

10

8.0

6.0

4.0

2.0

0

Vin, INPUT VOLTAGE (Vdc)

V

out

, OUTPUT

VOL

TAGE

(Vdc)

a

b

c

TA = + 125

°

C

TA = + 25

°

C

TA = – 55

°

C

A AND B CONNECTED TO Vin

ENABLE INPUT CONNECTED TO

VDD. OTHER INPUTS CONNECTED

TO VSS.

VDD = 15 Vdc

10 Vdc

5.0 Vdc

b

c

a

b

a

c

b

c

a

Summary of Contents for CMOS Logic

Page 1: ......

Page 5: ...iv MOTOROLA CMOS LOGIC DATA ...

Page 6: ...Master Index 1 ...

Page 12: ...Product Selection Guide 2 ...

Page 17: ...The Better Program 3 ...

Page 20: ...B and UB Series Family Data 4 ...

Page 25: ...CMOS Handling and Design Guidelines 5 ...

Page 32: ...CMOS Handling and Design Guidelines 5 ...

Page 39: ...Data Sheets 6 ...

Page 234: ...MOTOROLA CMOS LOGIC DATA MC14174B 6 196 FUNCTIONAL BLOCK DIAGRAM TIMING DIAGRAM ...

Page 238: ...MOTOROLA CMOS LOGIC DATA MC14175B 6 200 FUNCTIONAL BLOCK DIAGRAM TIMING DIAGRAM ...

Page 555: ...CMOS Reliability 7 ...

Page 561: ...Equivalent Gate Count 8 ...

Page 563: ...Packaging Information Including Surface Mounts 9 ...

Page 571: ......