MOTOROLA CMOS LOGIC DATA

MC14543B

6–384

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

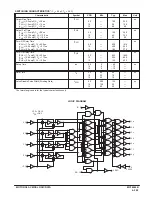

SWITCHING CHARACTERISTICS*

(CL = 50 pF, TA = 25

_

C)

Characteristic

Symbol

VDD

Min

Typ

Max

Unit

Output Rise Time

tTLH = (3.0 ns/pF) CL + 30 ns

tTLH = (1.5 ns/pF) CL + 15 ns

tTLH = (1.1 ns/pF) CL + 10 ns

tTLH

5.0

10

15

—

—

—

100

50

40

200

100

80

ns

Output Fall Time

tTHL = (1.5 ns/pF) CL + 25 ns

tTHL = (0.75 ns/pF) CL + 12.5 ns

tTHL = (0.55 ns/pF) CL + 12.5 ns

tTHL

5.0

10

15

—

—

—

100

50

40

200

100

80

ns

Turn–Off Delay Time

tPLH = (1.7 ns/pF) CL + 520 ns

tPLH = (0.66 ns/pF) CL + 217 ns

tPLH = (0.5 ns/pF) CL + 160 ns

tPLH

5.0

10

15

—

—

—

605

250

185

1210

500

370

ns

Turn–On Delay Time

tPHL = (1.7 ns/pF) CL + 420 ns

tPHL = (0.66 ns/pF) CL + 172 ns

tPHL = (0.5 ns/pF) CL + 130 ns

tPHL

5.0

10

15

—

—

—

505

205

155

1650

660

495

ns

Setup Time

tsu

5.0

10

15

350

450

500

—

—

—

ns

Hold Time

th

5.0

10

15

40

30

20

—

—

—

ns

Latch Disable Pulse Width (Strobing Data)

tWH

5.0

10

15

250

100

80

125

50

40

—

—

—

ns

* The formulas given are for the typical characteristics only.

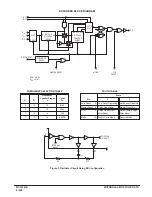

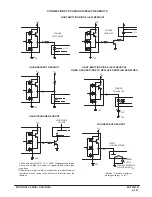

LOGIC DIAGRAM

VDD = PIN 16

VSS = PIN 8

B 3

LD 1

D 4

C 2

A 5

PHASE 6

14 g

15 f

13 e

12 d

11 c

10 b

9 a

BI 7

Summary of Contents for CMOS Logic

Page 1: ......

Page 5: ...iv MOTOROLA CMOS LOGIC DATA ...

Page 6: ...Master Index 1 ...

Page 12: ...Product Selection Guide 2 ...

Page 17: ...The Better Program 3 ...

Page 20: ...B and UB Series Family Data 4 ...

Page 25: ...CMOS Handling and Design Guidelines 5 ...

Page 32: ...CMOS Handling and Design Guidelines 5 ...

Page 39: ...Data Sheets 6 ...

Page 234: ...MOTOROLA CMOS LOGIC DATA MC14174B 6 196 FUNCTIONAL BLOCK DIAGRAM TIMING DIAGRAM ...

Page 238: ...MOTOROLA CMOS LOGIC DATA MC14175B 6 200 FUNCTIONAL BLOCK DIAGRAM TIMING DIAGRAM ...

Page 555: ...CMOS Reliability 7 ...

Page 561: ...Equivalent Gate Count 8 ...

Page 563: ...Packaging Information Including Surface Mounts 9 ...

Page 571: ......