REL0.2

Page 45 of 88

Zynq Ult MPSoC SBC Hardware User Guide

iWave Systems Technologies Pvt. Ltd.

2.9.1

PS Interfaces

The interfaces which are supported in Board to Board Connector1 from Zynq Ult

MPSoC’s PS is explained in

the following section.

2.9.1.1

SPI Interface

The Zynq Ult MPSoC SBC supports one SPI interface with one chip select on Board to Board Connector1. The

SPI0 controller

of MPSoC’s PS

is used for SPI interface through MIO pins. It can function in master mode, slave mode

or multi-master mode and supports full-duplex operation.

For more details on SPI Interface pinouts on Board to Board Connector1, refer the below table.

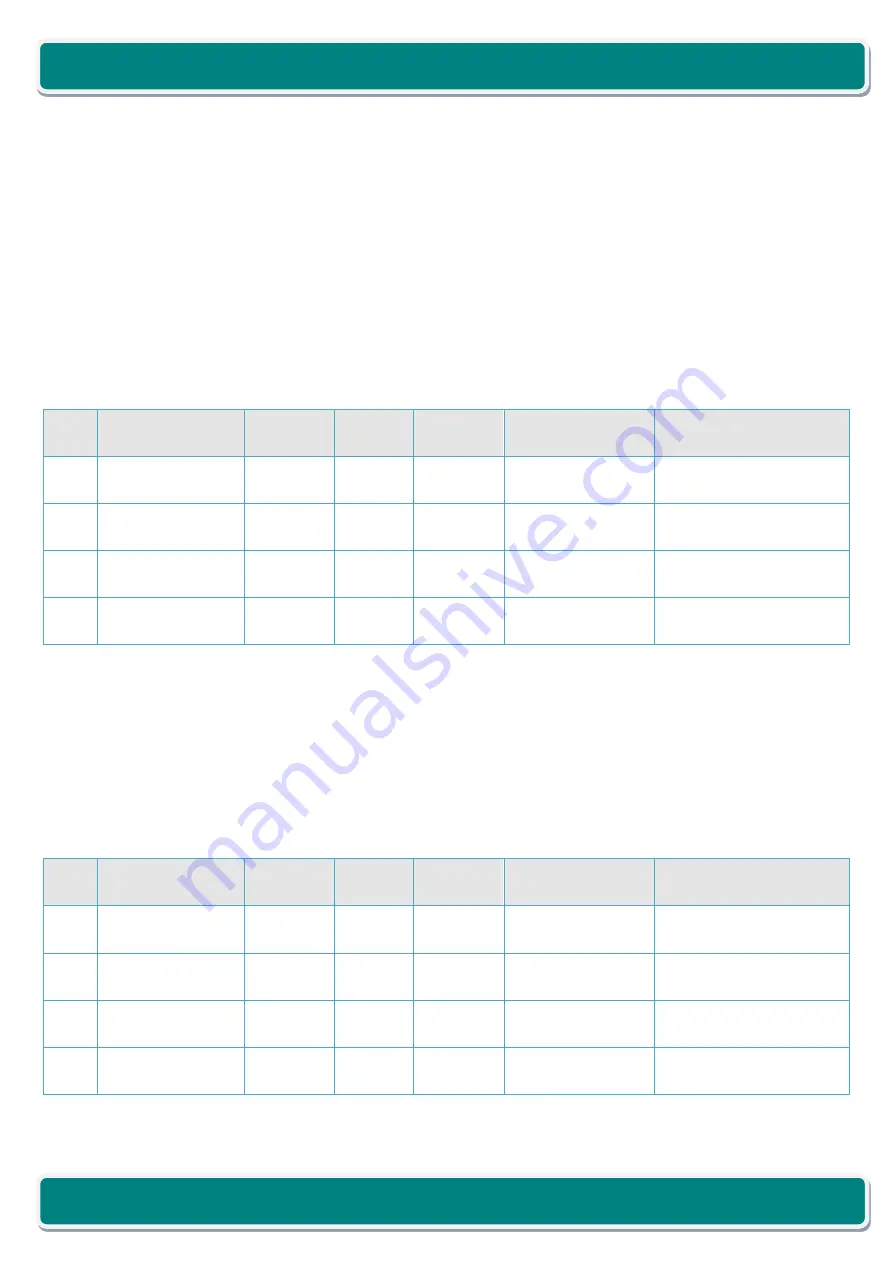

Pin

No

Signal Name

MPSoC Pin

Name

MPSoC

Bank

MPSoC Pin

No

Signal Type/

Termination

Description

14

SPI0_MISO(PS_MI

O4_500)

PS_MIO4_

500

500

AH16

IO, 1.8V LVCMOS

SPI Master input Slave

output.

16

SPI0_MOSI(PS_MI

O5_500)

PS_MIO5_

500

500

AD16

IO, 1.8V LVCMOS

SPI Master output Slave

input.

18

SPI0_SS0(PS_MIO3

_500)

PS_MIO3_

500

500

AH15

O, 1.8V LVCMOS

SPI chip select0.

20

SPI0_SCLK(PS_MIO

0_500)

PS_MIO0_

500

500

AG15

O, 1.8V LVCMOS

SPI clock.

2.9.1.2

CAN Interface

The Zynq Ult MPSoC SBC supports two CAN interfaces on Board to Board Connector1. The CAN0 & CAN1

controller of

MPSoC’s

PS is used for CAN interface through MIO pins. This CAN controller is compatible with the ISO

11898-1, CAN 2.0A, and CAN 2.0B standards. And it supports bit rates up to 1Mb/s.

For more details on CAN Interface pinouts on Board to Board Connector1, refer the below table.

Pin

No

Signal Name

MPSoC Pin

Name

MPSoC

Bank

MPSoC Pin

No

Signal Type/

Termination

Description

28

CAN1_RX(PS_MIO4

1_501)

PS_MIO41

_501

501

J19

I, 1.8V LVCMOS

CAN1 Receive data.

32

CAN1_TX(PS_MIO4

0_501)

PS_MIO40

_501

501

K18

O, 1.8V LVCMOS

CAN1 Transmit data.

30

CAN0_TX(PS_MIO3

9_501)

PS_MIO39

_501

501

H19

O, 1.8V LVCMOS

CAN0 Transmit data.

34

CAN0_RX(PS_MIO3

8_501)

PS_MIO38

_501

501

H19

I, 1.8V LVCMOS

CAN0 Receive data.