5-6

BRC-300/300P

BRU-300/300P

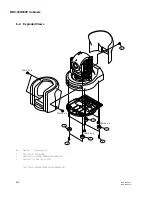

5-4. BRBK-301 (AN-22 Board) Circuit

Description

The BRBK-301 is installed in BRC-300/300P or BRU-

300/300P to output analog GBR/YCbCr/SYNC signals and

analog composite/YC signals to the 9-pin D-sub connector.

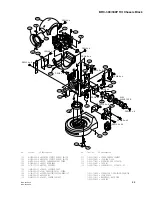

Analog GBR/YCbCr/SYNC Signals

The 8-bit Y data and CbCr data sent from BRC-300/300P

or BRU-300/300P are latched by the 13.5 MHz clock and

6.75 MHz clock, and then separated into 8-bit Y/Cb/Cr

data of the same timing. These data are converted to analog

Y/Cb/Cr signals by D/A converters IC7011, IC7012 and

IC7013, and then decoded to analog G/B/R signals by

IC7016, IC7017 and IC7018.

Selectors IC7024, IC7025 and IC7026 select either one of

the analog Y/Cb/Cr signals or analog G/B/R signals. A

sync signal is added to the Y signal or G/B/R signals by

IC7028, IC7029 and IC7030. The Y signal or G/B/R

signals are then output to the D-sub connector. It is also

possible to output G/B/R signals without sync signal. The

sync signal is the C SYNC signal sent from BRC-300/300P

or BRU-300/300P, which is also output to the D-sub

connector.

Analog VBS/YC Signals

The 8-bit Y data and CbCr data sent from BRC-300/300P

or BRU-300/300P are input into the digital encoder

IC7022.

The digital encoder encodes the Y and CbCr data to the

composite signal and Y/C signals using the 27 MHz clock

and H SYNC/V SYNC signals, and then converts the

digital signals to analog composite signals and Y/C signals.

Either one of the analog composite signal or analog Y/C

signals is selected by the selectors IC7032 and IC7033, and

then output to the D-sub connector.

Output Signal Selection and Level Adjustment

The serial data CSO sent from BRC-300/300P or BRU-

300/300P is D/A converted by EVR IC7015 to restore

selection signals and level adjustment signals. These

signals are used for selection of analog output signals and

for level adjustment.

Power Supply Circuit

The DC-DC converter generates

+

3.3 V DC and

_

3.3 V

DC from the

+

12 V supplied by BRC-300/300P or BRU-

300/300P.

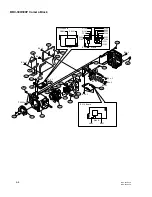

5-5. BRBK-302 (SD-50 Board) Circuit

Description

The BRBK-302 is installed in BRC-300/300P or BRU-

300/300P to output the SDI signal.

The 8-bit Y data and CbCr data sent from BRC-300/300P

or BRU-300/300P are multiplexed by IC8003. Synchroniz-

ing data is also added based on the FLD, VD and HD

signals. The multiplexed data is then converted to SDI

serial data by IC8006, and then output to external equip-

ments with the output drivers Q8006 and Q8007.

The flash memory IC8005 retains the configuration data of

the FPGA IC8003.

The DC-DC converter generates

+

3.3 V DC and

+

5 V DC

from the

+

12 V supplied by BRC-300/300P or BRU-300/

300P. Further, the series regulator generates

+

1.5 V DC

from the

+

3.3 V.