7-3

BRC-300/300P

BRU-300/300P

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

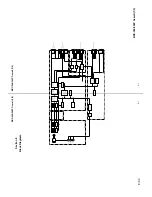

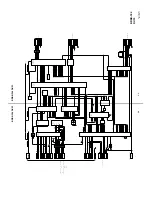

CANNEL LINK TRANSMITTER

—TOP VIEW—

: TTL LEVEL CLOCK

: TTL LEVEL DATA

: POWER DOWN

: POSITIVE LVDS DIFFERENTIAL CLOCK

: NEGATIVE LVDS DIFFERENTIAL CLOCK

: POSITIVE LVDS DIFFERENTIAL DATA

: NEGATIVE LVDS DIFFERENTIAL DATA

: GROUND FOR LVDS

: POWER SUPPLY FOR LVDS

: GROUND FOR PLL

: POWER SUPPLY FOR PLL

LVDS-TO-TTL PARALLEL

PLL

TXCLK OUT

+

TXCLK OUT

_

37

38

39

40

41

42

45

46

TXOUT 0

+

TXOUT 0

_

TXOUT 1

+

TXOUT 1

_

TXOUT 2

+

TXOUT 2

_

TXOUT 3

+

TXOUT 3

_

47

48

TXIN0 - TXIN27

TXCLK IN

31

28

INPUTS

TXCLK IN

TXIN0 - TXIN27

PWRDOWN

OUTPUTS

TXCLK OUT

+

TXCLK OUT

_

TXOUT0

+

- TXOUT3

+

TXOUT0

_

- TXOUT3

_

OTHERS

LVDS GND

LVDS V

CC

PLL GND

PLL V

CC

51, 52, 54 - 56,

2 - 4, 6 - 8,

10 - 12, 14 - 16,

18 - 20, 22 - 25,

27, 28,

30, 50

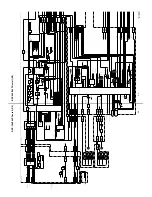

WRITE

DATA

REGISTER

INPUT

BUFFER

8

8

OUTPUT

BUFFER

INTERNAL

BUS

CONTROL

BUS

ADDRESS

BUS

INTERNAL

BUS

TIMING

AND LOGIC

CONTROL

READ

DATA

REGISTER

512 k

X

8

MEMORY

CELL ARRAY

MEMORY

CONTROL

REFRESH

COUNTER

TO ALL MODULES

IRDY

WCK

WRST

IE

WE

15

13

14

11

10

DI0 - DI7

1 - 4,

6 - 9

SDA

SCL

SDAEN

25

24

23

PLRTY

RESET

16

27

INPUT

CONTROL

TIMING

GENERATOR

AND

ARBITER

ORDY

RCK

RRST

OE

RE

30

32

31

34

35

DO0 - DO7

36 - 39,

41 - 44

OUTPUT

CONTROL

CONTROL

REGISTERS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

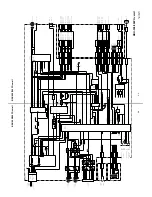

4 M (512 k

X

8) -BIT FIFO FIELD MEMORY

—TOP VIEW—

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

DI0

DI1

DI2

DI3

V

CC

DI4

DI5

DI6

DI7

WE

IE

GND

WCK

WRST

IRDY

PLRTY

TEST

A.V

CC

NC

NC

NC

A.GND

I

I

I/O

—

I

—

—

O

I

I

—

SDAEN

SCL

SDA

GND

RESET

NC

V

CC

ORDY

RRST

RCK

GND

I

I

O

O

O

O

—

O

O

O

O

OE

RE

DO7

DO6

DO5

DO4

V

CC

DO3

DO2

DO1

DO0

I

I

I

I

—

I

I

I

I

I

I

—

I

I

O

I

I

—

—

—

—

—

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

1

2

3

4

5

6

7

8

9

10

11

INPUTS

DI0 - DI7

IE

OE

PLRTY

RCK

RE

RESET

RRST

SCL

SDAEN

TEST

WCK

WE

WRST

OUTPUTS

DO0 - DO7

IRDY

ORDY

INPUT/OUTPUT

SDA

OTHER

NC

: DATA

: INPUT SIGNAL ENABLE

: OUTPUT SIGNAL ENABLE

: ACTIVE POLARITY SELECT

: READ CLOCK

: READ ENABLE

: RESET

: READ ADDRESS RESET

: SERIAL BUS CLOCK

: SERIAL BUS INTERFACE ENABLE

: TEST

: WRITE CLOCK

: WRITE ENABLE

: WRITE ADDRESS RESET

: DATA

: FIFO SPACE AVAILABILITY STATUS

: FIFO DATA AVAILABILITY STATUS

: SERIAL BUS DATA

: NO CONNECTION

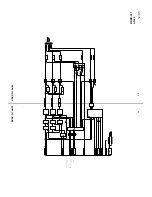

IC

[|IC|]

AL440B-24PBF (AVER LOGIC)

DS90CR287MTDX (NS)

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

15

16

17

18

19

20

21

22

23

24

25

26

27

28

TXIN15

TXIN16

V

CC

TXIN17

TXIN18

TXIN19

GND

TXIN20

TXIN21

TXIN22

TXIN23

V

CC

TXIN24

TXIN25

29

30

31

32

33

34

35

36

37

38

39

40

41

42

—

I

I

I

—

—

—

—

O

O

O

O

O

O

GND

TXIN26

TXCLK IN

PWRDOWN

PLL GND

PLL V

CC

PLL GND

LDVS GND

TXOUT3

+

TXOUT3

_

TXCLKOUT

+

TXCLKOUT

_

TXOUT2

+

TXOUT2

_

43

44

45

46

47

48

49

50

51

52

53

54

55

56

—

—

O

O

O

O

—

I

I

I

—

I

I

I

LDVS GND

LDVS V

CC

TXOUT1

+

TXOUT1

_

TXOUT0

+

TXOUT0

_

LDVS GND

TXIN27

TXIN0

TXIN1

GND

TXIN2

TXIN3

TXIN4

—

I

I

I

—

I

I

I

—

I

I

I

—

I

I

I

—

I

I

I

—

I

I

I

I

—

I

I

1

2

3

4

5

6

7

8

9

10

11

12

13

14

V

CC

TXIN5

TXIN6

TXIN7

GND

TXIN8

TXIN9

TXIN10

V

CC

TXIN11

TXIN12

TXIN13

GND

TXIN14

TXIN5

_

1

TXOUT3

TXCLK

PREVIOUS CYCLE

NEXT CYCLE

TXIN27

_

1

TXIN23

TXIN17

TXIN16

TXIN11

TXIN10

TXIN5

TXIN27

TXIN20

_

1

TXOUT2

TXIN19

_

1

TXIN26

TXIN25

TXIN24

TXIN22

TXIN21

TXIN20

TXIN19

TXIN9

_

1

TXOUT1

TXIN8

_

1

TXIN18

TXIN15

TXIN14

TXIN13

TXIN12

TXIN9

TXIN8

TXIN1

_

1

TXOUT0

TXIN0

_

1

TXIN7

TXIN6

TXIN4

TXIN3

TXIN2

TXIN1

TXIN0