18 UNIVERSAL SERIAL INTERFACE (USI)

S1C33L26 TECHNICAL MANUAL

Seiko Epson Corporation

18-11

0x0

Address

0x6

0x2

0x2

Transfer data 1

A6

A5

D7

D6

D5

D4

D3

D2

D1

D0

A4

A3

A2

A1

A0 R/W = 0

ACK

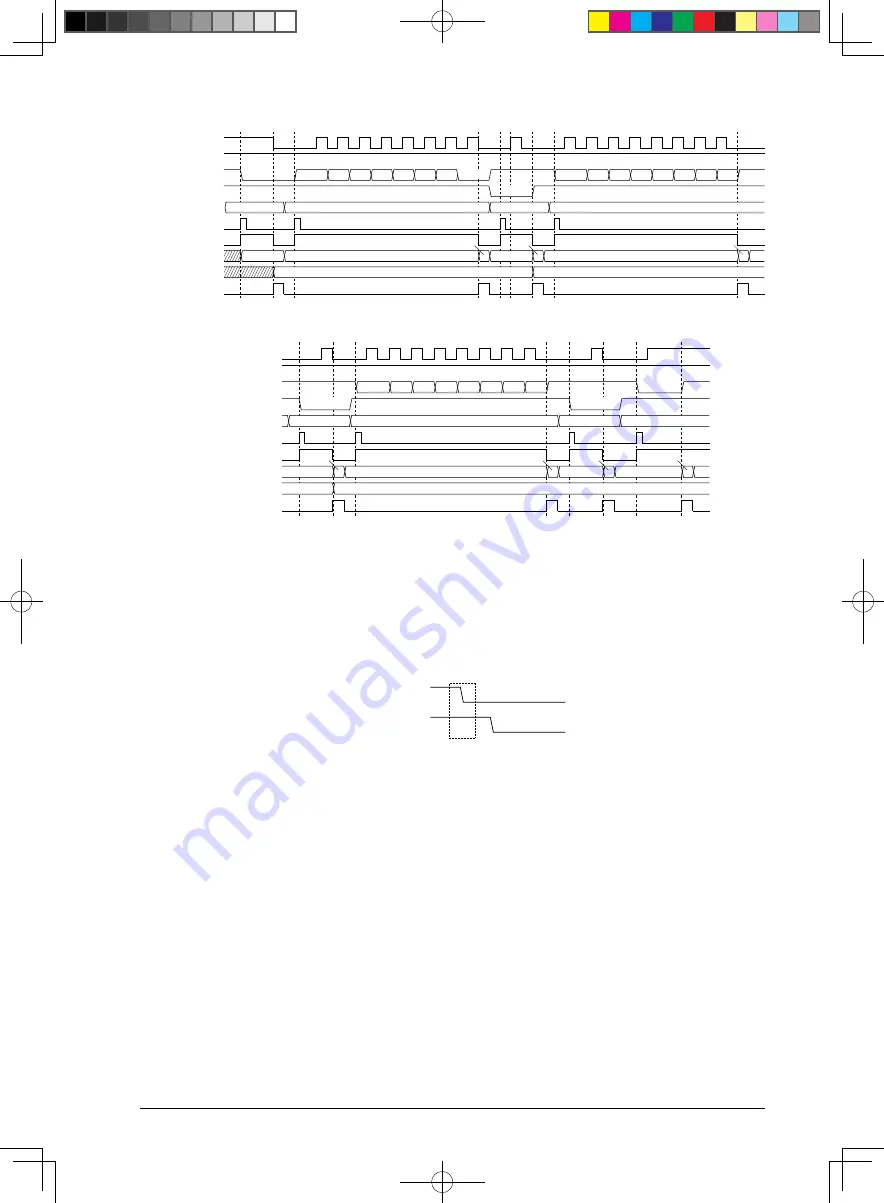

USI_CK pin (output)

USI_CK pin (input)

USI_DI pin (output)

USI_DI pin (input)

IMTGMOD[2:0]

IMTG (write)

IMBSY

IMSTA[2:0]

TD[7:0]

IMIF

Start interrupt

End of transmission

interrupt

End of transmission

interrupt

Receive

ACK interrupt

0x0

*

*

*

*

0x2

0x5

0x2

(1) Start condition

→

Data transmission

0x6

0x6

0x2

0x1

Transfer data n

D7

D6

D5

D4

D3

D2

D1

D0

ACK

ACK

USI_CK pin (output)

USI_CK pin (input)

USI_DI pin (output)

USI_DI pin (input)

IMTGMOD[2:0]

IMTG (write)

IMBSY

IMSTA[2:0]

TD[7:0]

IMIF

Stop interrupt

End of transmission

interrupt

Receive

ACK interrupt

Receive

ACK interrupt

*

*

*

*

*

0x2

0x1

0x5

0x5

(2) Data transmission

→

Stop condition

*

When IMIF is cleared via software, IMSTA[2:0] is also cleared to 0x0.

5.3.2 I

Figure 18.

2

C Master Data Transmission Timing Chart

(1) Generating start condition

I

2

C data transfer starts when the I

2

C master device generates a start condition. The start condition applies

when the SCL line is maintained at high and the SDA line is pulled down to low.

To generate a start condition in this I

2

C master, set IMTGMOD[2:0] to 0x0 (default) and write 1 to IMTG.

SDA (USI_DI)

SCL (USI_CK)

Start condition

5.3.3 Start Condition

Figure 18.

IMBSY is set to 1 while a start condition is being generated. When the start condition is generated, IMBSY

is reset to 0 and IMSTA[2:0] is set to 0x0. The I

2

C bus is busy from this point on.

Note: Other operations cannot be started before a start condition is generated.

(2) Sending slave address and transfer direction bit

After a start condition has been generated, send the address of the slave device to be communicated and a

transfer direction bit. I

2

C slave addresses are either 7-bit or 10-bit. This module uses an 8-bit transfer data

buffer to send the slave address and transfer direction bit, enabling single transfers in 7-bit address mode. In

10-bit mode, data is sent twice or three times under software control. Figure 18.5.3.4 shows the configura-

tion of the address data.